TechSource Systems is MathWorks Authorised Reseller and Training Partner

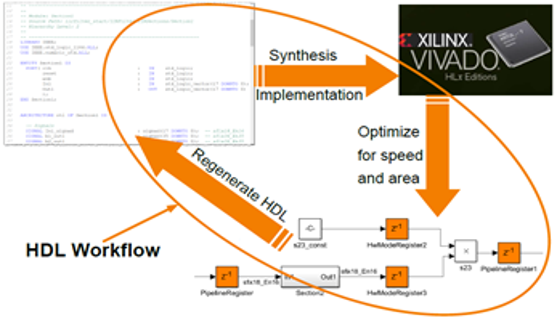

Learn to prepare Simulink models for HDL code generation, generate HDL code, and optimize Simulink models

Complimentary Services: Post training email support & 1-hr consultation session within 1 month after the course completion!

This two-day course shows how to generate and verify HDL code from a Simulink® model using HDL Coder™ and HDL Verifier™.

Topics include:

Engineers who wish to design and simulate their system with Simulink and accelerate the implemention to FPGA by using HDL Coder.

Signal Processing with Simulink or equivalent experience using Simulink.

Upon the completion of the course, the participants will be able to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

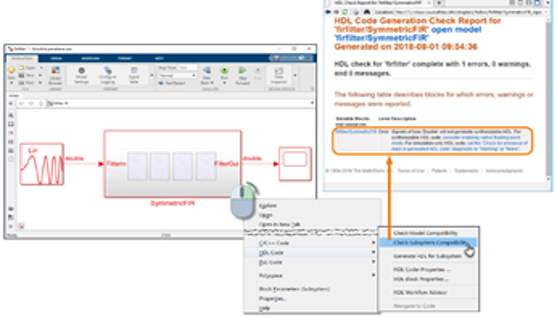

Objective: Prepare a Simulink model for HDL code generation. Generate HDL code and testbench for simple models requiring no optimization.

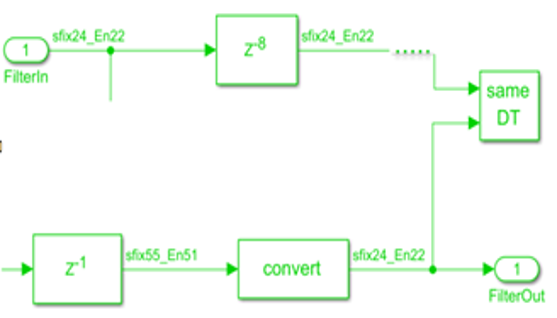

Objective: Establish correspondence between generated HDL code and specific Simulink blocks in the model. Use Fixed-Point Tool to finalize fixed point architecture of the model.

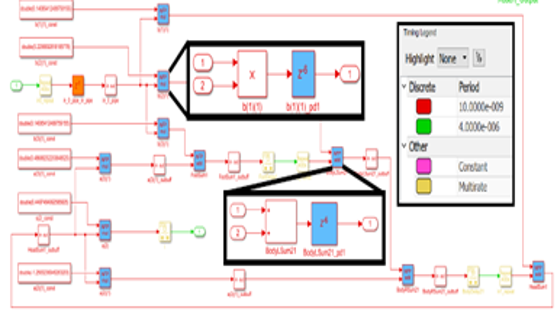

Objective: Generate HDL code for multirate designs.

Objective: Use pipelines to meet design timing requirements. Use specific hardware implementations and share resources for area optimization.

Objective: Implement floating point values and operations in your HDL code.

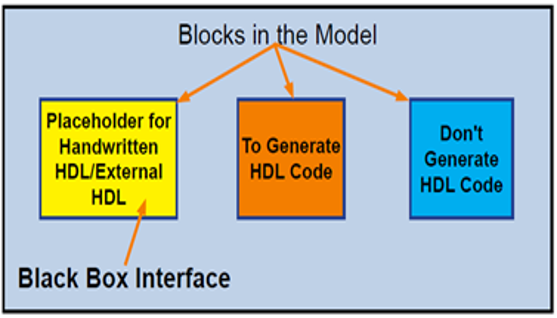

Objective: Incorporate hand-written HDL code and/or vendor party IP in your design.

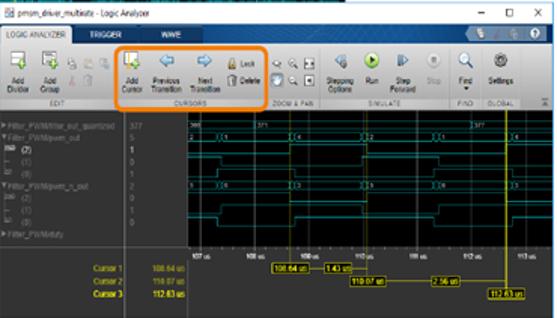

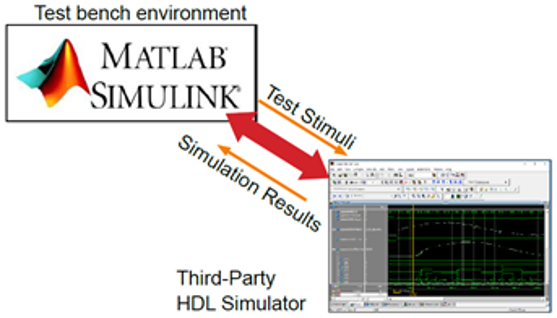

Objective: Verify your HDL code using an HDL simulator in the Simulink model.