TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn general embedded concepts, tools, and techniques using the

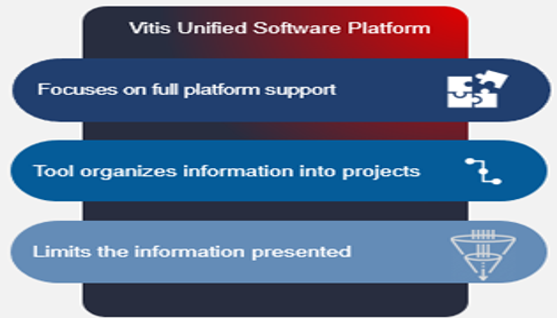

Vivado® Design Suite and Vitis™ unified software platform.

This two-day training let you Learn general embedded concepts, tools, and techniques using the Vivado® Design Suite and Vitis™ unified software platform.

The emphasis is on:

What’s New for 2021.2

Engineers who are interested in developing embedded systems with the Xilinx Zynq SoC, Zynq UltraScale+ MPSoC, and/or MicroBlaze soft processor core.

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

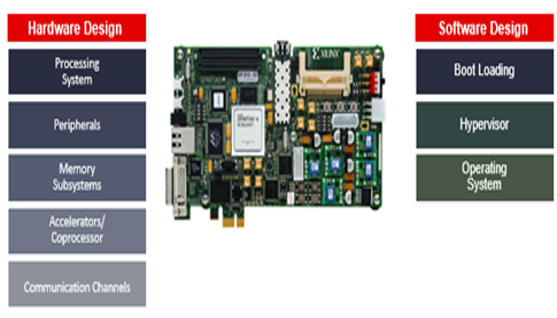

Objective: Outlines the different elements that comprise the Embedded Design Methodology.

Objective: Overview of the embedded hardware development flow.

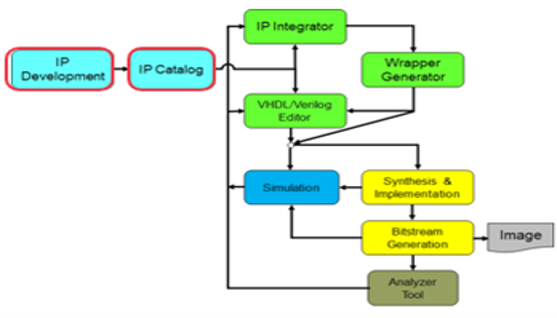

Objective: Describes how to access and effectively use the IPI tool.

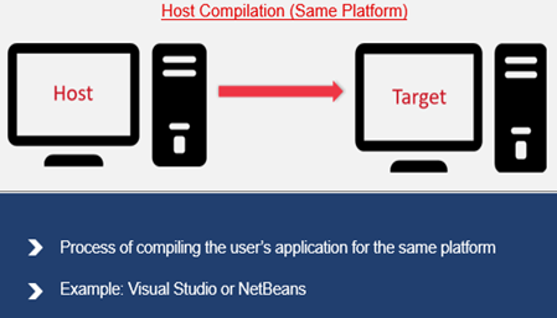

Objective: Reviews the process of building a user application.

Objective: Introduces the basic behaviors required to drive the Vitis tool to generate a debuggable C/C++ application.

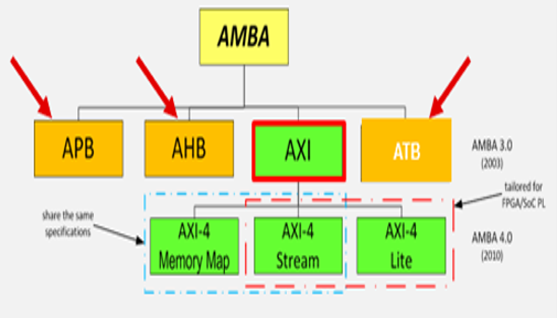

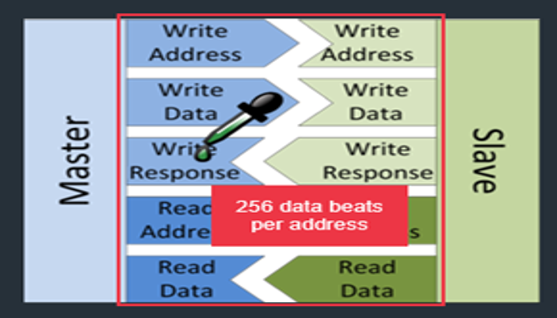

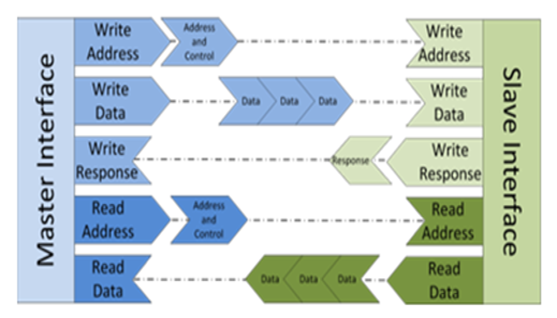

Objective: Introduces the AXI protocol.

Objective: Describes the differences and similarities among the three

primary AXI variations.

Objective: Describes the differences and similarities among the three

primary AXI variations.

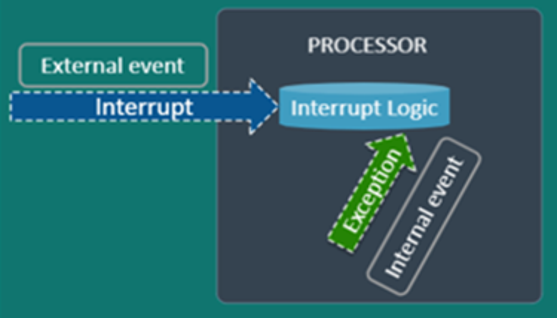

Objective: Explain the difference between an interrupt and an exception.

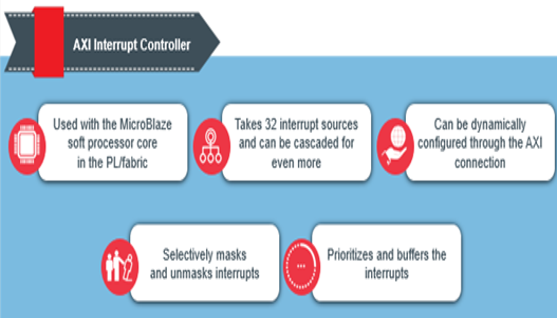

Objective: Reviews the hardware that is typically available to help implement and manage interrupts.

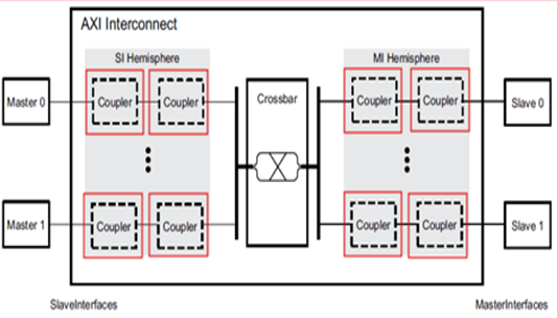

Objective: Describes the relationships between different types of AXI interfaces and how they can be connected to form hierarchies.

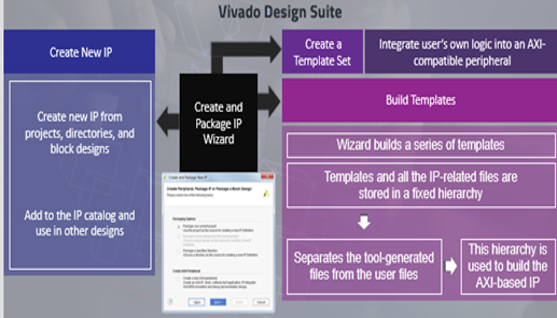

Objective: Explains how to use the Create and Import Wizard to create and package an AXI IP.

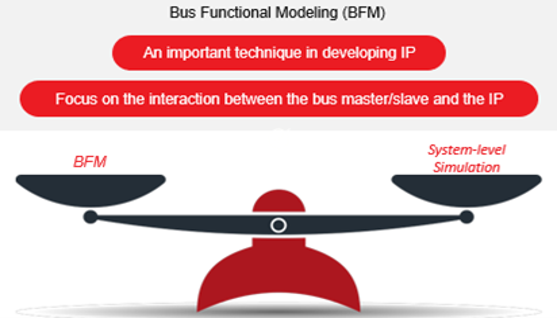

Objective: Describes how to perform BFM simulation using the Verification IP.

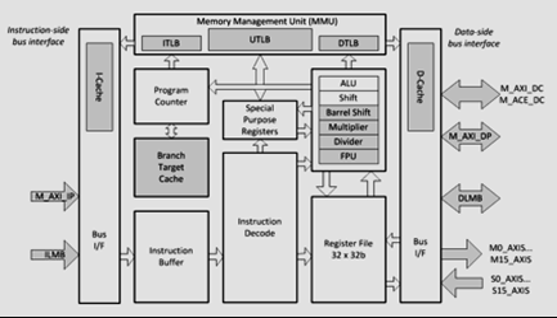

Objective: Overview of the MicroBlaze microprocessor architecture.

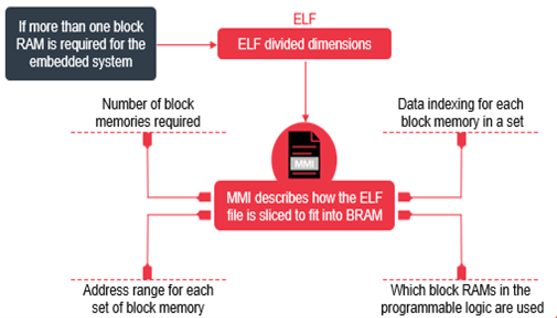

Objective: Highlights how block RAM can be used with the MicroBlaze processor.

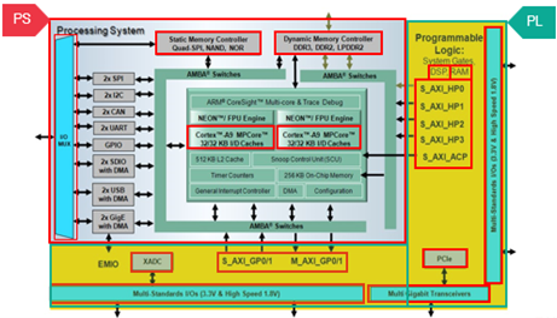

Objective: Overview of the Zynq-7000 SoC architecture.

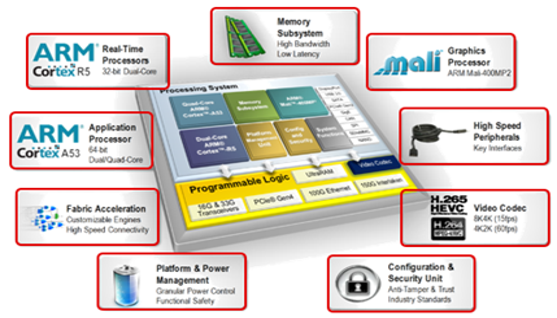

Objective: Overview of the Zynq UltraScale+ MPSoC architecture.