TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn general embedded concepts, tools, and techniques using the

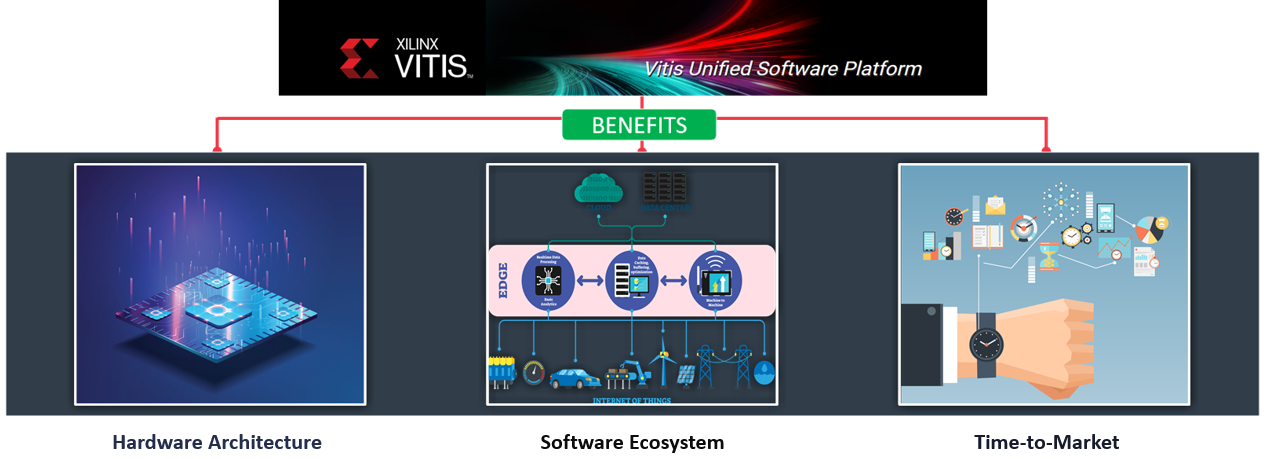

Vivado® Design Suite and Vitis™ unified software platform with a special emphasis on the RF Data Converter

This four-day training let you Learn general embedded concepts, tools, and techniques using the Vivado® Design Suite and Vitis™ unified software platform.

The emphasis is on:

Engineers who are interested in developing embedded systems with the Zynq UltraScale+ MPSoC. and interested in understanding the architecture and capabilities of the Zynq UltraScale+ RFSoC data converter.

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

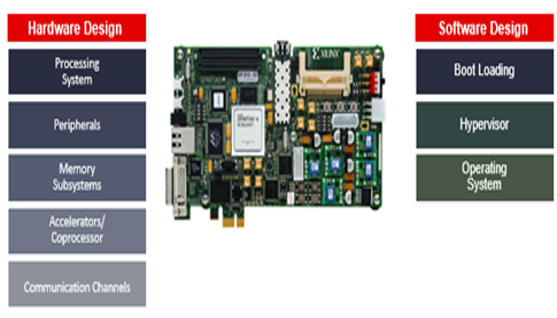

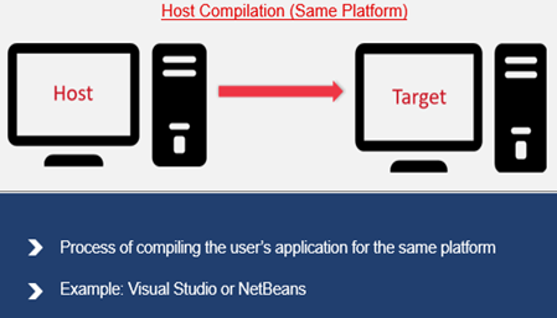

Objective: Outlines the different elements that comprise the Embedded Design Methodology.

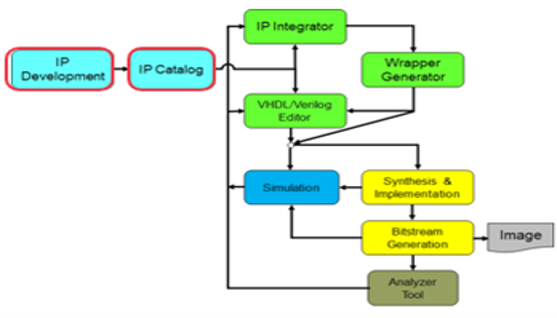

Objective: Overview of the embedded hardware development flow.

Objective: Describes how to access and effectively use the IPI tool.

Objective: Reviews the process of building a user application.

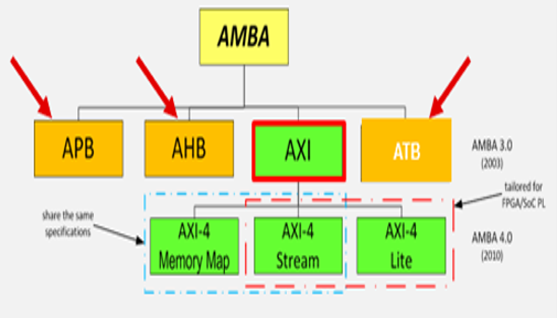

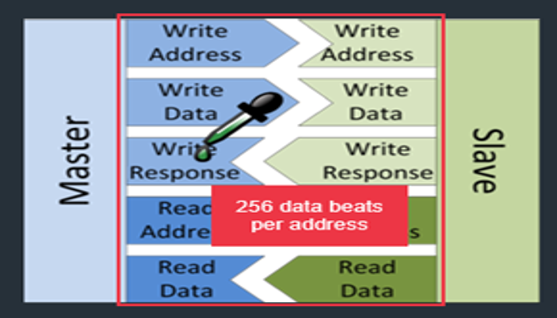

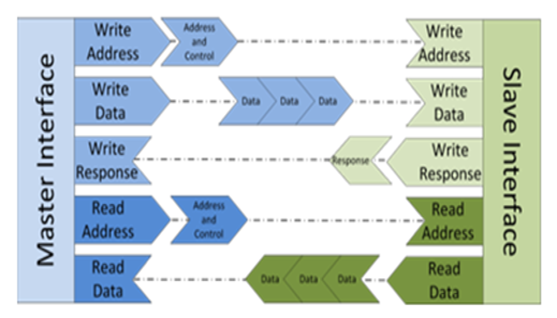

Objective: Introduces the AXI protocol.

Objective: Describes the differences and similarities among the three primary AXI variations.

Objective: Describes the differences and similarities among the three primary AXI variations.

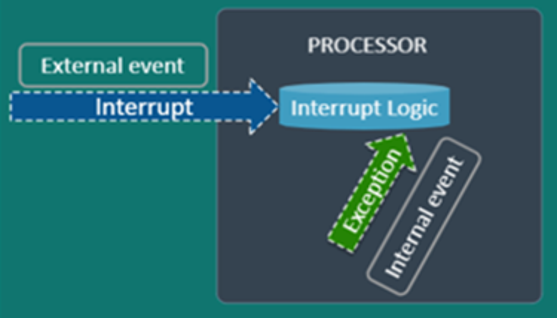

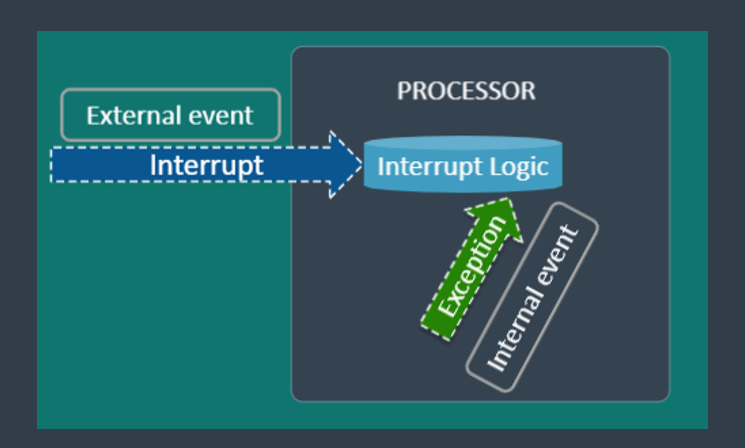

Objective: Explain the difference between an interrupt and an exception.

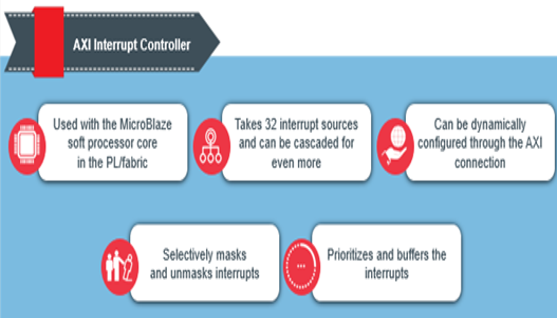

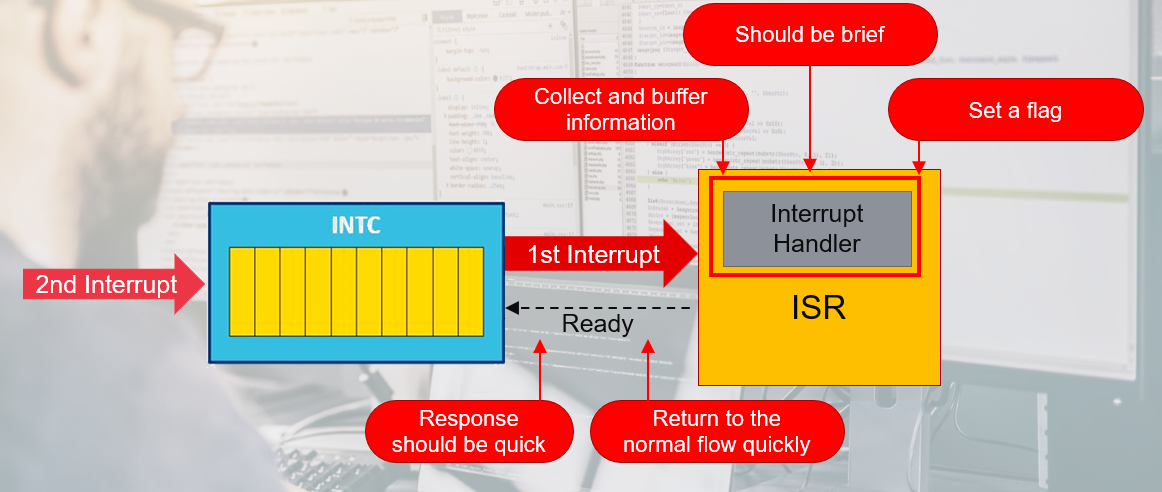

Objective: Reviews the hardware that is typically available to help implement and manage interrupts.

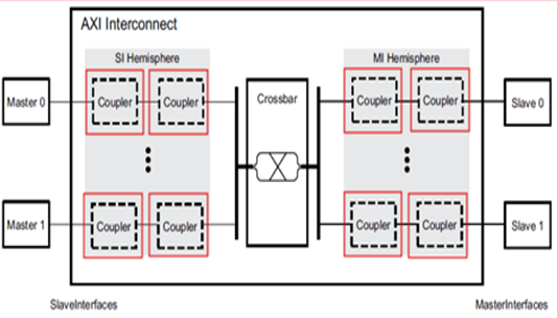

Objective: Describes the relationships between different types of AXI interfaces and how they can be connected to form hierarchies.

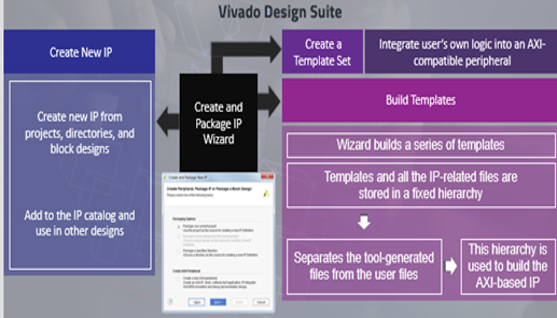

Objective: Explains how to use the Create and Import Wizard to create and package an AXI IP.

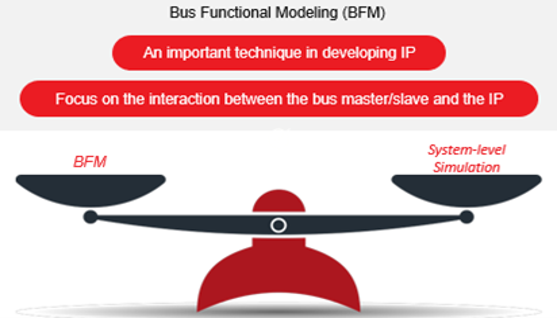

Objective: Describes how to perform BFM simulation using the Verification IP.

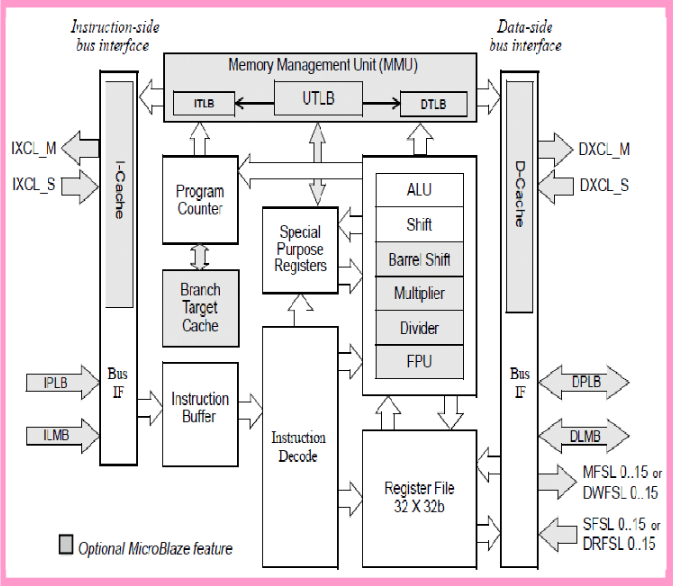

Objective: Overview of the MicroBlaze microprocessor architecture.

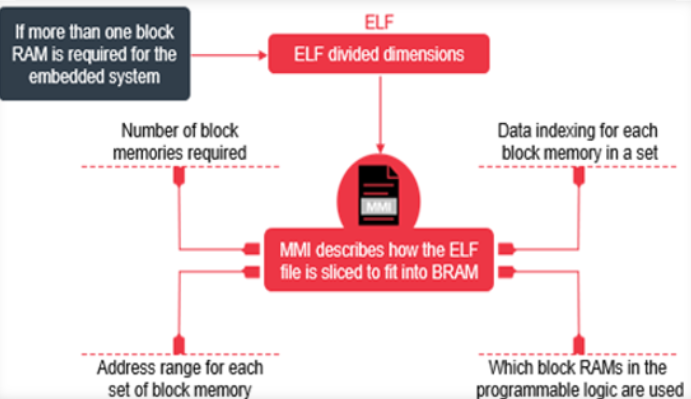

Objective: Highlights how block RAM can be used with the MicroBlaze processor.

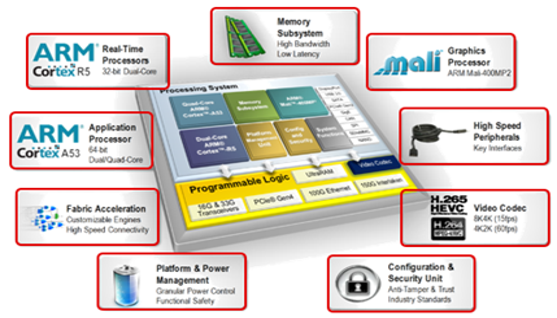

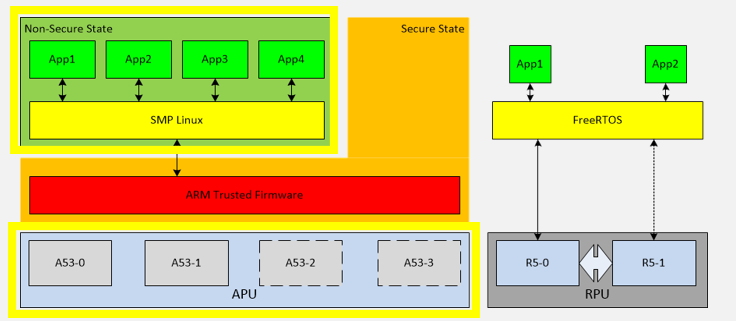

Objective: Overview of the Zynq UltraScale+ MPSoC architecture.

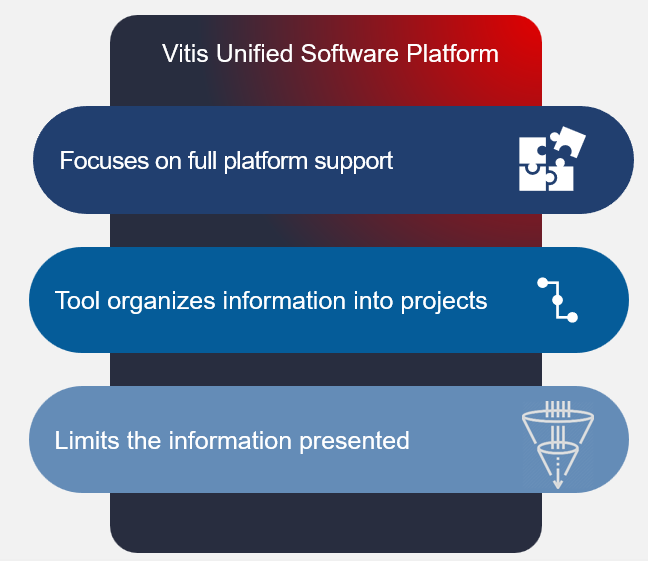

Objective: Enumerate some of the under-the-hood tools provided in the Vitis IDE.

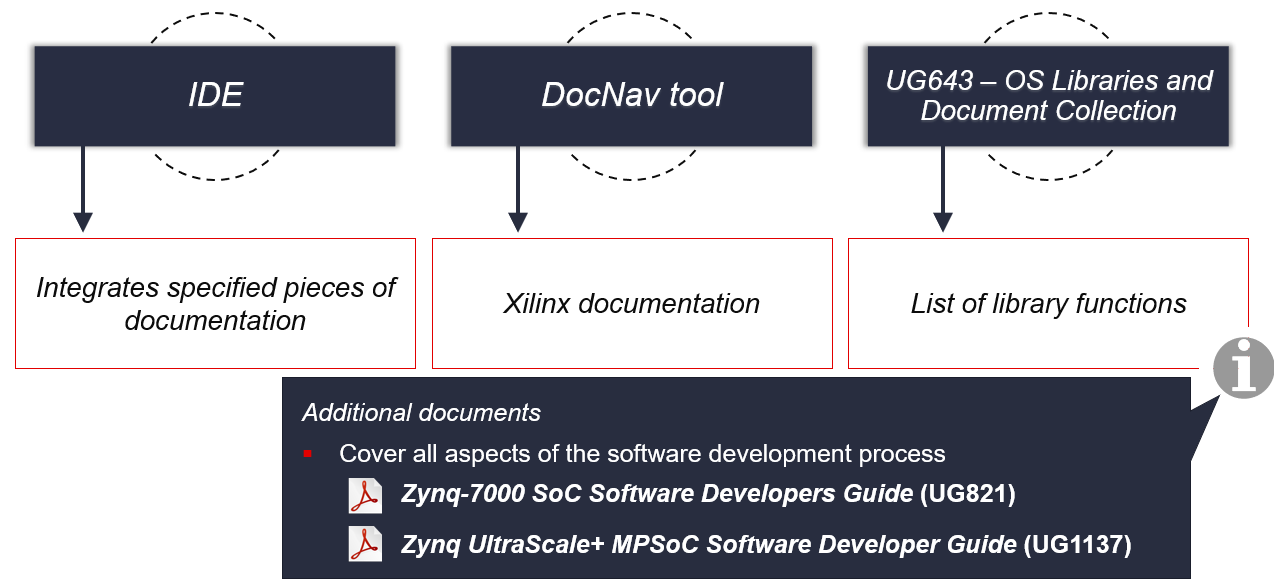

Objective: Describes the software development environments for Zynq UltraScale+™ MPSoCs.

Objective: Introduces the basic behaviors required to drive the Vitis tool to generate a debuggable C/C++ application.

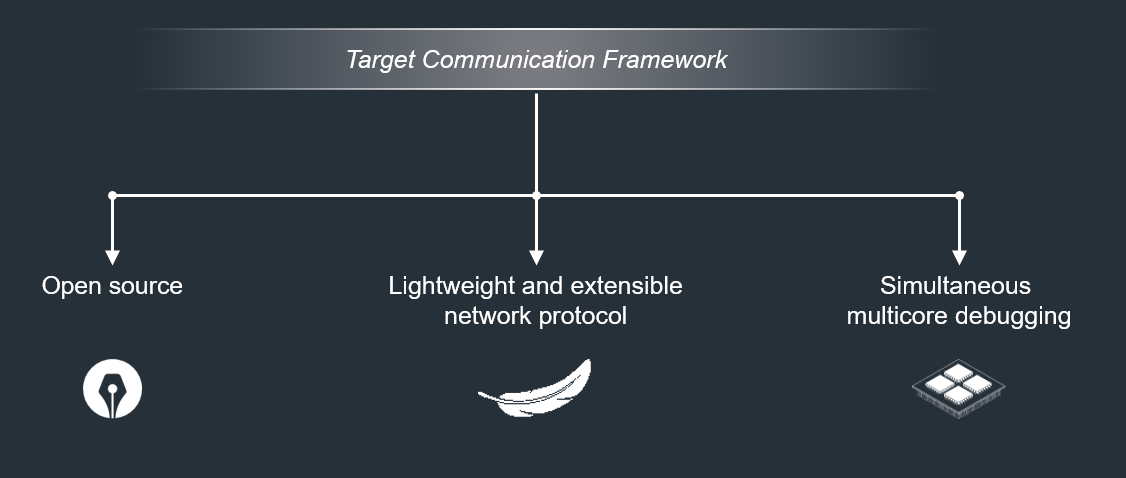

Objective: Describes the basics of actually running a debugger and illustrates the most commonly used debugging commands.

Objective: Covers the various software components, or layers, supplied by AMD that aid in the creation of low-level software and includes a discussion on drivers, domains, operating systems, and libraries. Also covers the basic services (libraries) available when coding in the Standalone environment.

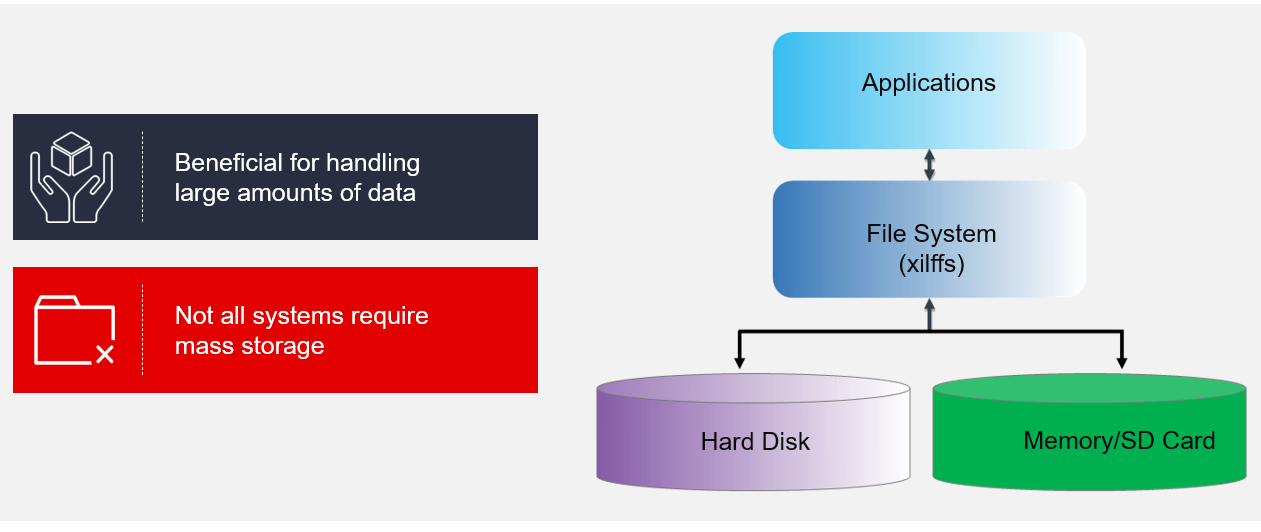

Objective: Introduces the FAT file system (FFS) from the Standalone/Bare-metal library. The FFS provides drivers and utilities for effectively converting a region of memory into a file system.

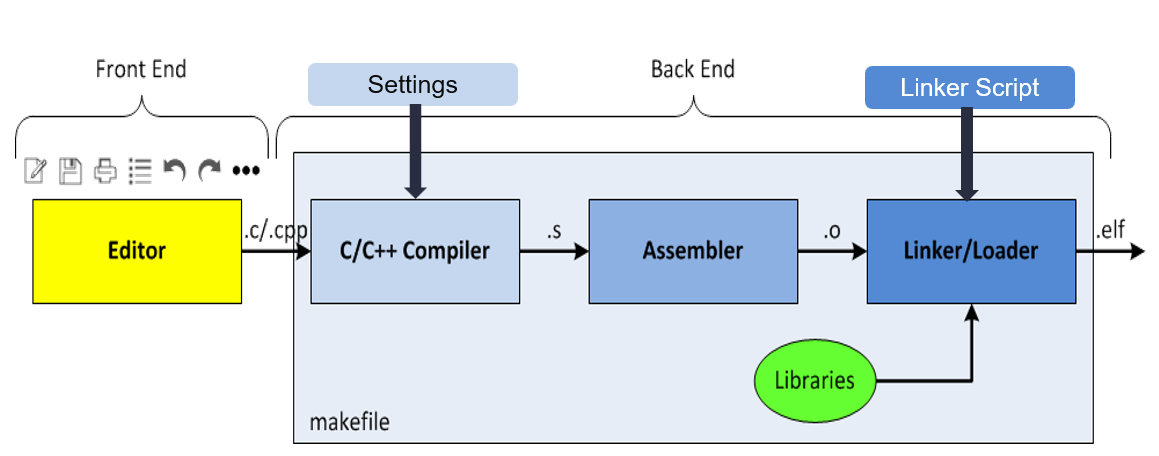

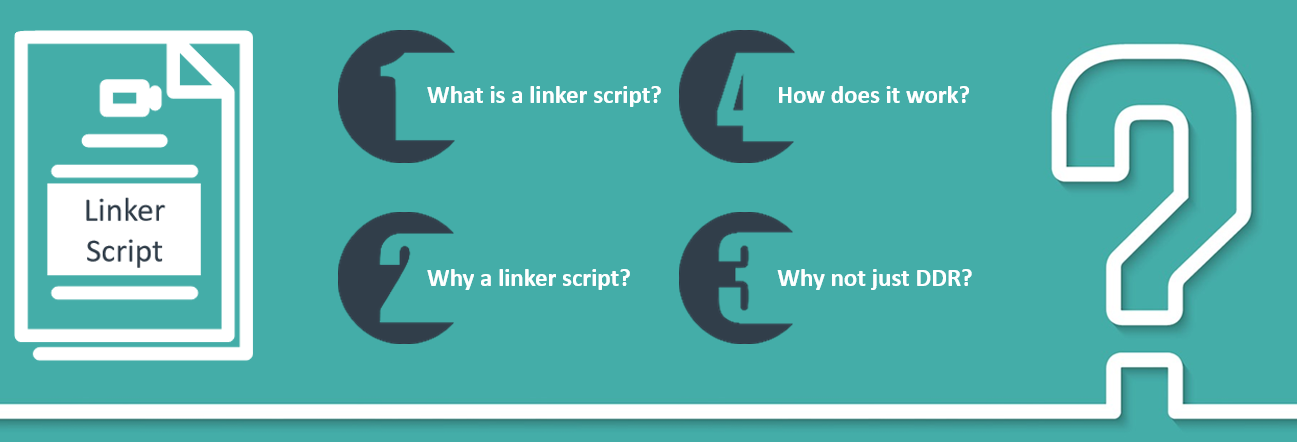

Objective: Overview of the purpose and typical use of a linker script.

Objective: Overview of migrating existing Xilinx SDK projects to Vitis software development projects.

Objective: Introduces the concept of interrupts, basic terminology, and generic implementation.

Objective: Describes many of the considerations that a software coder must take into account when supporting interrupts.

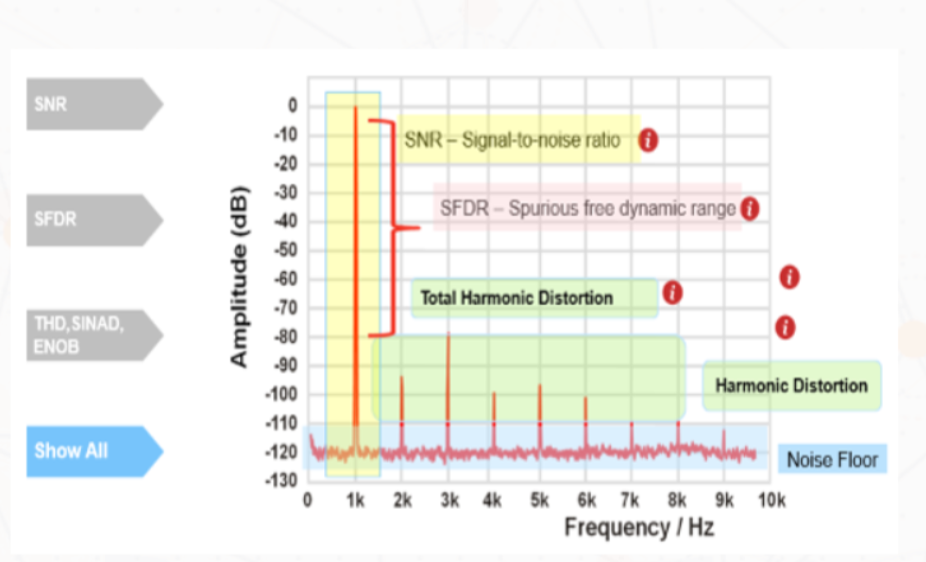

Objective: Covers the basics of RF-ADCs. Reviews RF-ADC architecture, functionality, interfaces, configuration, and driver support.

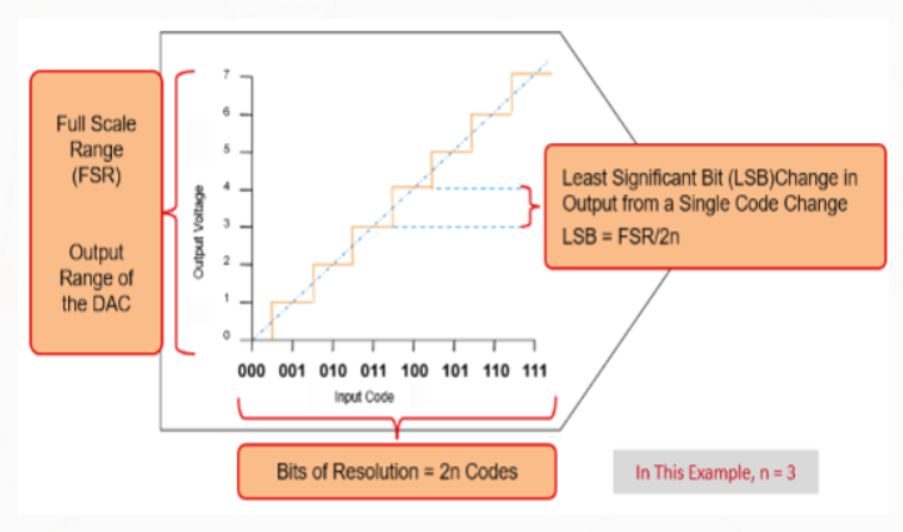

Objective: Covers the basics of RF-DACs. Reviews RF-DAC architecture, functionality, interfaces, configuration, and driver support.