TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn how to employ serial transceivers in UltraScale and UltraScale+ FPGA designs or Zynq UltraScale+ MPSoC designs

The focus of this two-day training is on:

This hands-on course is designed for FPGA Designers and logic designers.

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

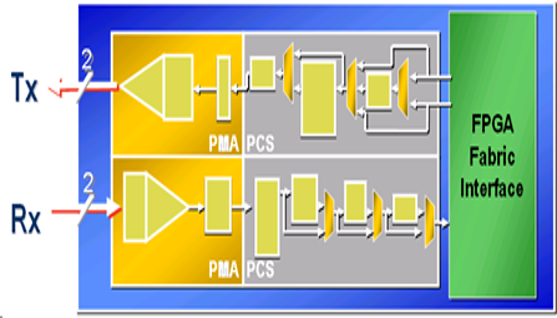

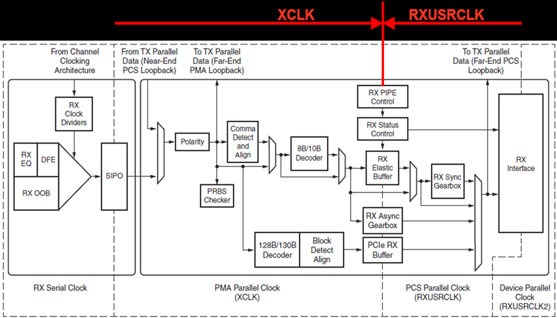

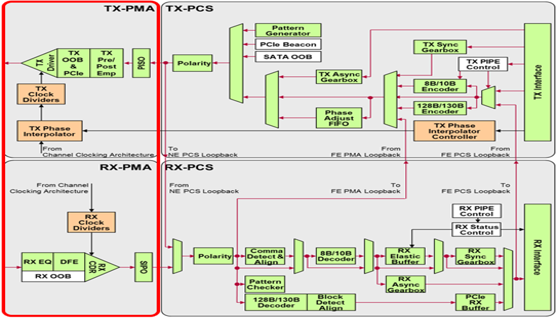

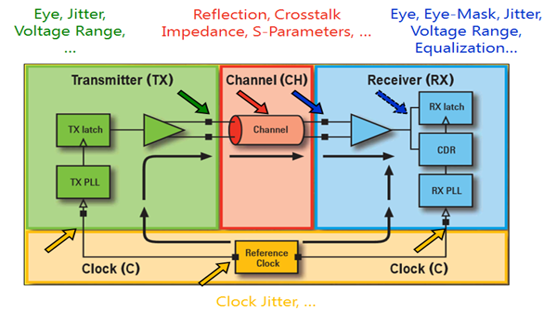

Objective: Provide an overview of the GT transceivers in UltraScale™ FPGAs. Describe the main features of the serial transceiver, the GT_QUAD tile, the GT transmitter architecture and functionality, the GT receiver architecture and functionality.

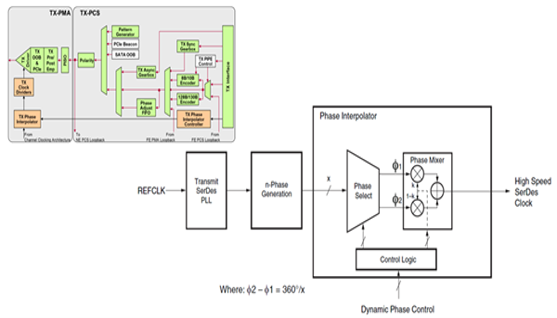

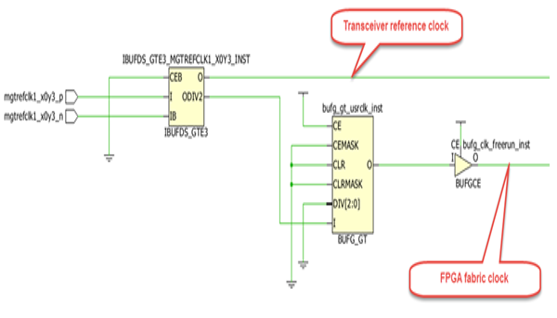

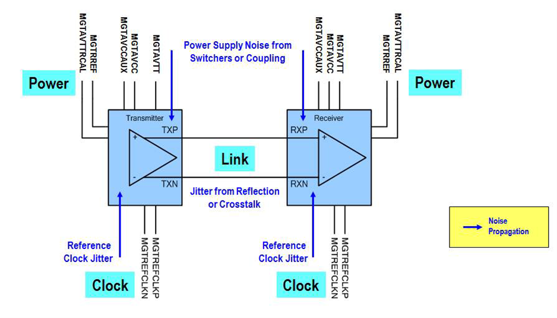

Objective: Describe the sources for transceiver reference clock signals and how to set the PLL attributes to create transceiver clocks. User clocks and reset signals are also described. Identify the three possible sources for GT reference clock signals. Set the PLL attributes to create internal GT clocks. Define each of the user clocks and their specific functions.

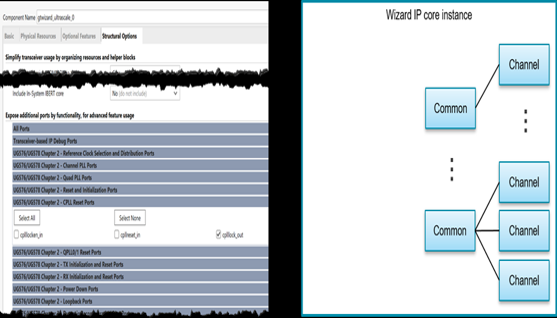

Objective: provide an overview of the 7 Series and UltraScale™ FPGA Transceivers Wizard. Describe the features of the Transceivers Wizard. Use the Transceivers Wizard to configure and instantiate GT primitives in an HDL design. Explain the usage of the transceiver IP example design.

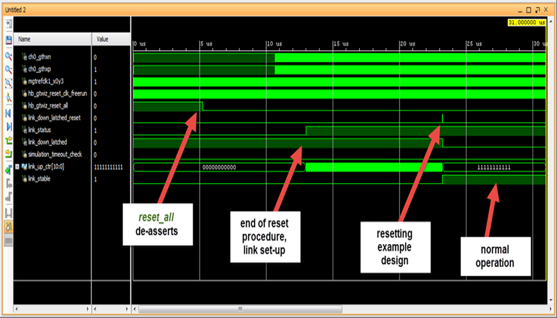

Objective: Describe the processes for simulating a design with serial transceivers. Describe simulation options. Compile serial transceiver models for simulation. Describe how to perform transceiver design simulation.

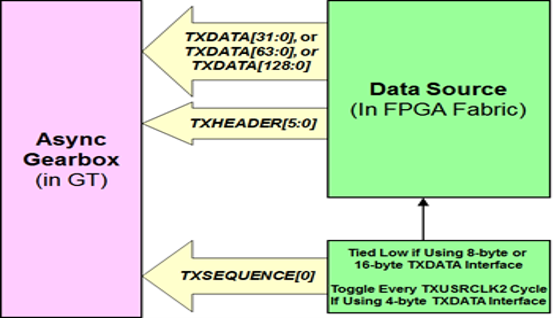

Objective: Discuss the Transceiver PCS Layer details for 7 series and UltraScale™ FPGAs. Describe the main features of PCS blocks. Describe the transceiver PCS functionality. Describe the usage options of PCS layer blocks.

Objective: Discuss the Transceiver PCS Layer details for 7 series and UltraScale™ FPGAs. Describe the main features of PCS blocks. Describe the transceiver PCS functionality. Describe the usage options of PCS layer blocks.

Objective: Describe the processes for implementing a design with serial transceivers. List the guidelines for channel bonding placement. Write timing constraints for serial transceiver clocks. Implement a design containing serial transceivers. Change serial transceiver attributes in the Device Viewer.

Objective: Describe special features for transmitting and receiving for the physical media attachment layer. Describe the special features of the transceiver TX PMA layer. Describe the special features of the transceiver RX PMA layer. List the parameters for optimizing a transceiver link.

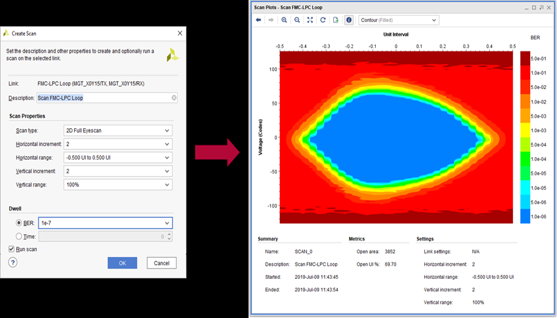

Objective: Describe options to validate and optimize the PMA layer parameters. Identify the possibilities for link optimization. Use various integrated bit error ratio test (IBERT) options to validate serial transceiver links.

Objective: Cover transceiver testing and debugging in 7 series and UltraScale™ FPGAs. Identify the possibilities for serial transceiver test and debugging. Use transceiver internal test options. Use debug cores for transceiver test and debug. Describe hardware measurement options.

Objective: Describe the power requirements of the GT transceiver, lists some guidelines for trace routing and signal integrity, and explains the need for GT link simulation on the board level. Describe the power requirements of the GT transceiver. List some guidelines for trace routing and signal integrity.

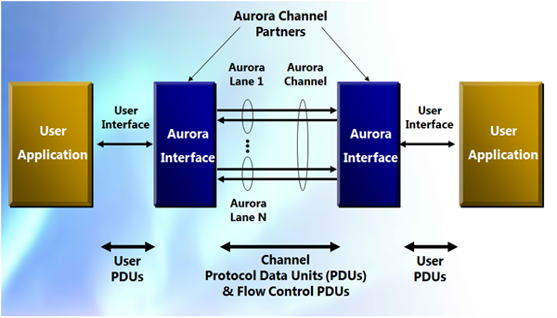

Objective: Describe how serial transceivers apply to special applications, focusing on Aurora, Networking IPs, Interlaken, PCI Express®, and JESD204 technologies. Describe main serial transceiver applications. Use the serial transceiver in application specific IPs.