TechSource Systems is MathWorks Authorised Reseller and Training Partner

Comprehensive Introduction to the VHDL Language

This three-day course provides a thorough introduction to the VHDL language.

The emphasis is on:

What’s New for 2021.1

Engineers who want to use VHDL effectively for modeling, design, and synthesis of digital designs.

Basic digital design knowledge.

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

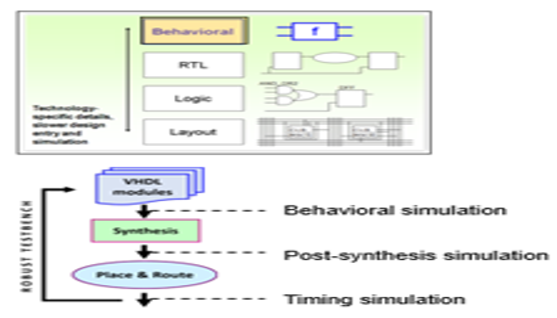

Objective: Discusses the history of the VHDL language and provides an overview of the different features of VHDL.

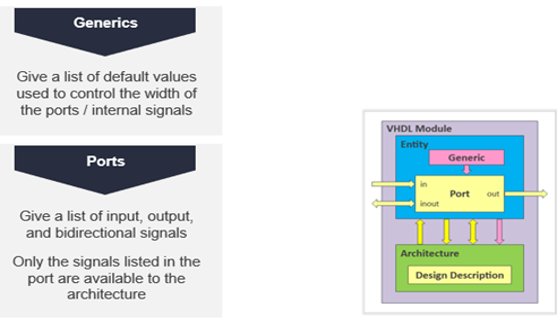

Objective: Provides an overview of typical VHDL code, covering design units such as libraries, packages, entities, architectures, and configuration.

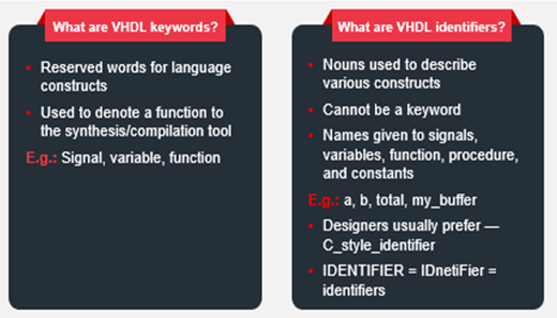

Objective: VHDL Objects, Keywords, Identifiers.

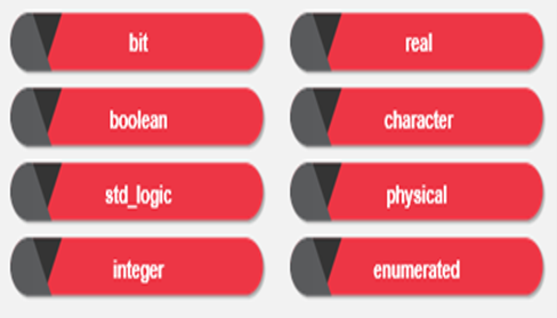

Objective: Covers both intrinsic and commonly used data types.

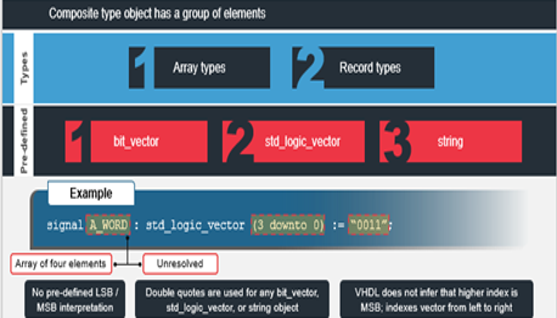

Objective: Covers composite data types (arrays and records).

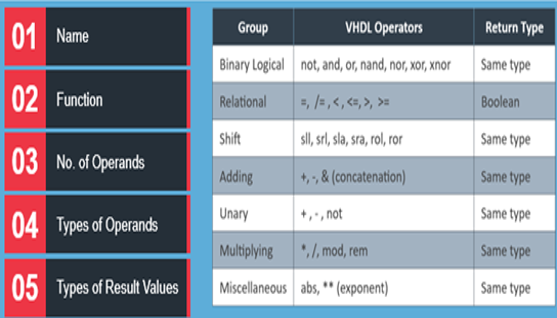

Objective: Reviews all VHDL operator types.

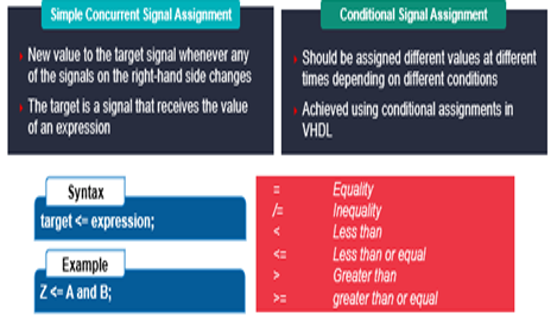

Objective: Describes concurrent statements and how signals help in achieving concurrency.

Objective: Covers both conditional and unconditional assignments.

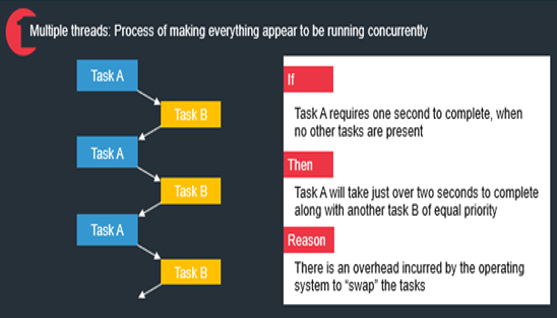

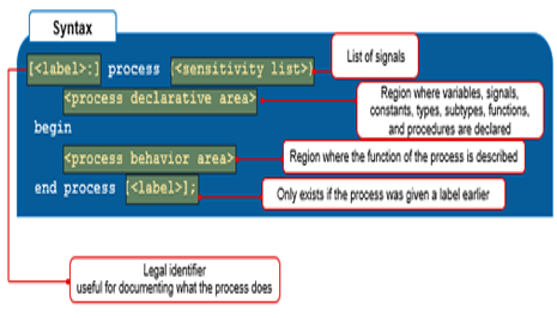

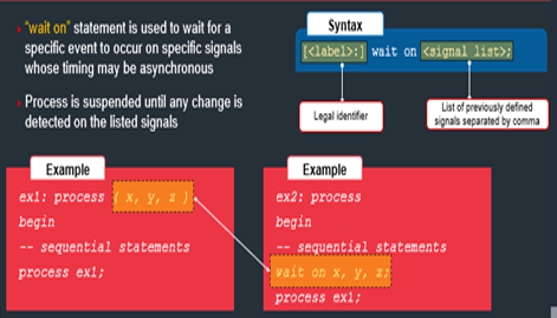

Objective: Introduces sequential programming techniques for a concurrent language. Variables are also discussed.

Objective: Covers both conditional and unconditional assignments.

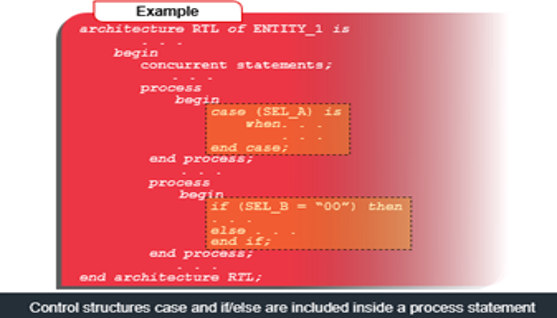

Objective: Describes conditional statements such as if/else and case statements.

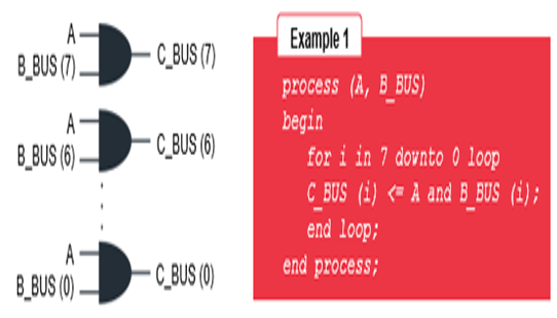

Objective: Introduces the concept of looping in both the simulation and synthesis environments.

Objective: Describes conditional statements such as if/else and case statements.

Objective: Introduces the concept of the VHDL testbench to verify the functionality of a design.

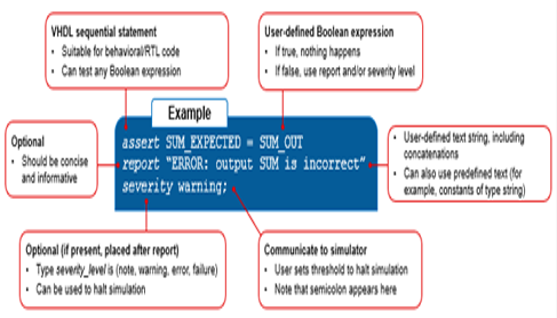

Objective: Describes the concept of VHDL assertions.

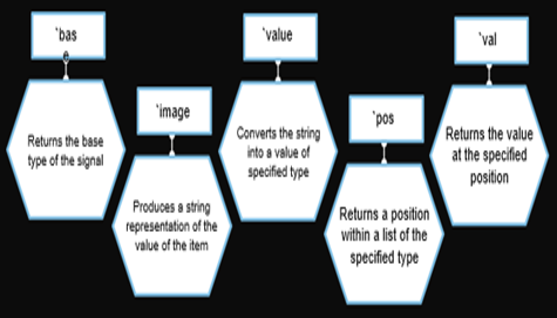

Objective: Describes attributes, both predefined and user defined.

Objective: Covers the use of subprograms in verification and RTL code to model functional blocks.

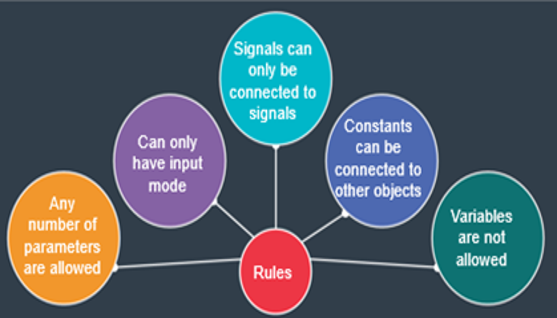

Objective: Describes functions, which are integral to reusable and

maintainable code.

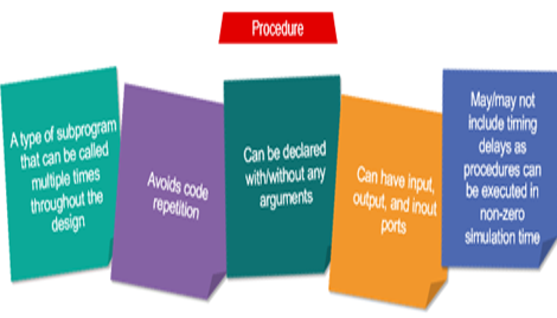

Objective: Describes procedures, common constructs that are also important for reusing and maintaining code.

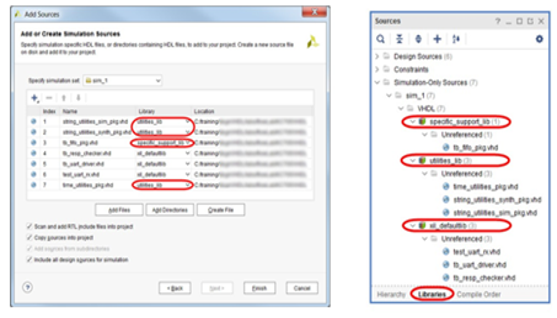

Objective: Demonstrates how libraries and packages are declared and used.

Objective: Describes how to interact with a simulation via text I/O.

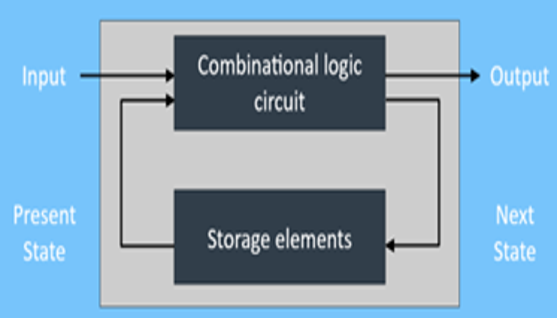

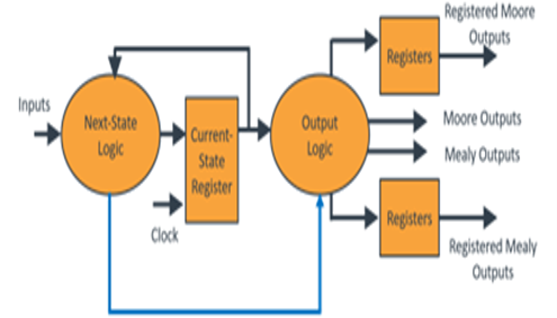

Objective: Provides an overview of finite state machines, one of the more commonly used circuits.

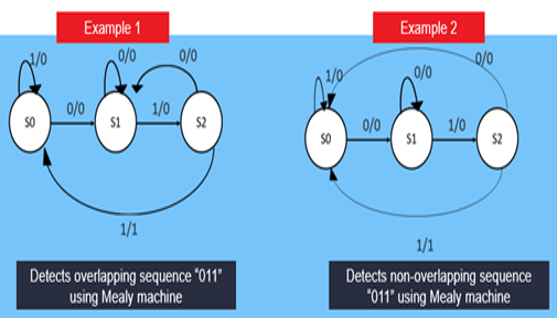

Objective: Describes how to implement a Mealy state machine in which the output is dependent on both the current state and the inputs.

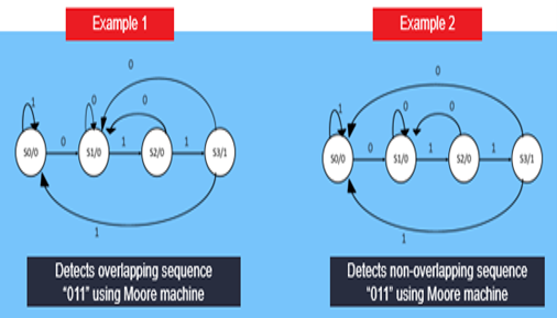

Objective: Demonstrates how to implement a Moore state machine in which the output is dependent on the current state only.

Objective: Describes the guidelines and recommendations for using one or more procedural blocks when coding a finite state machine.

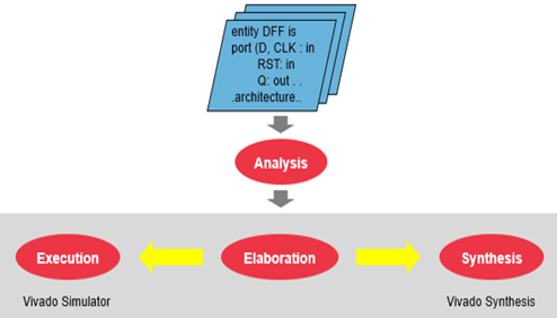

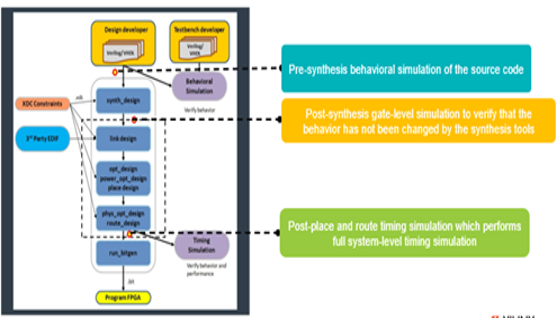

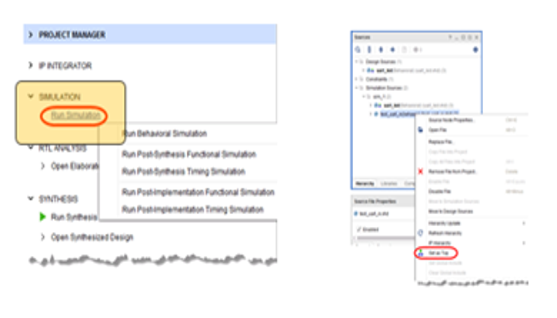

Objective: Introduces the Vivado simulator simulation environment. Race conditions are also discussed.

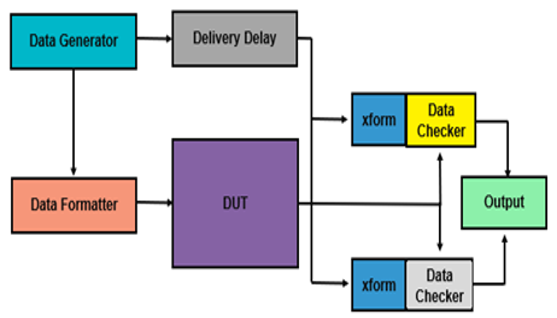

Objective: Explores how time-agnostic, self-checking testbenches can be written and applied.

Objective: Focuses on Xilinx-specific implementation and chip-level optimization.