TechSource Systems is MathWorks Authorised Reseller and Training Partner

The UltraScale™ and UltraScale+™ architectures to both new and experienced designers.

This course introduces the UltraScale™ and UltraScale+™

architectures to both new and experienced designers.

The emphasis is on:

What’s New for 2021.2

Anyone who would like to build a design for the UltraScale or UltraScale+ device family.

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

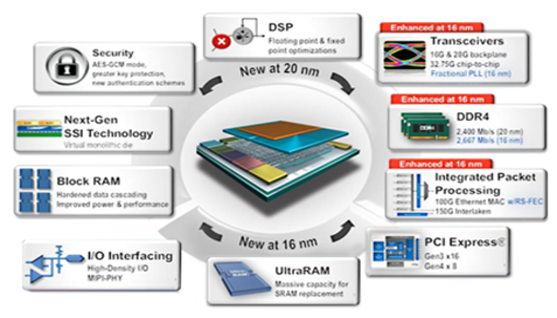

Objective: Review the UltraScale architecture, which includes enhanced CLB resources, DSP resources, etc.

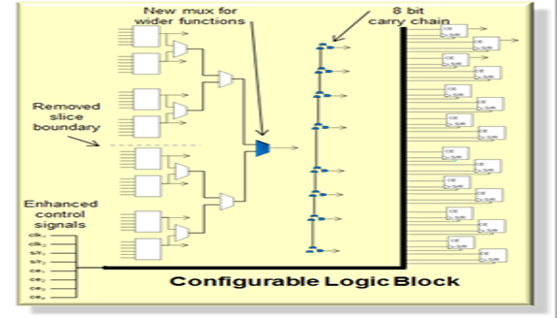

Objective: Examine the CLB resources, such as the LUT and the dedicated carry chain, in the UltraScale architecture.

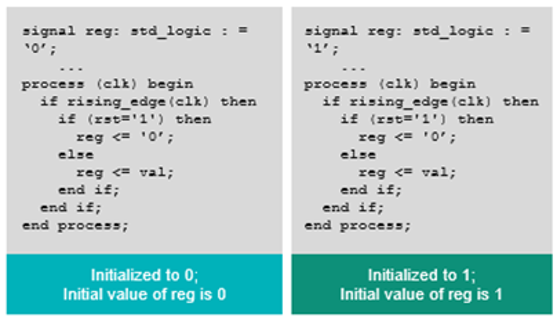

Objective: Cover basic digital coding guidelines used in an FPGA design.

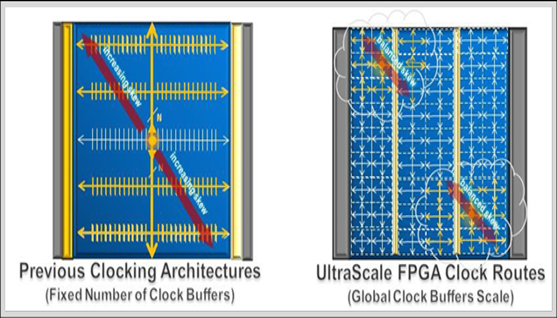

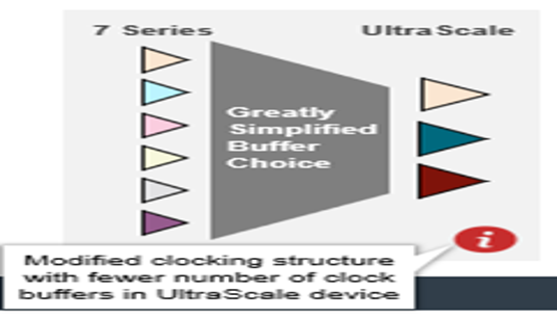

Objective: Use the Clocking Wizard to configure a clocking subsystem to provide various clock outputs and distribute them on the dedicated global clock networks.

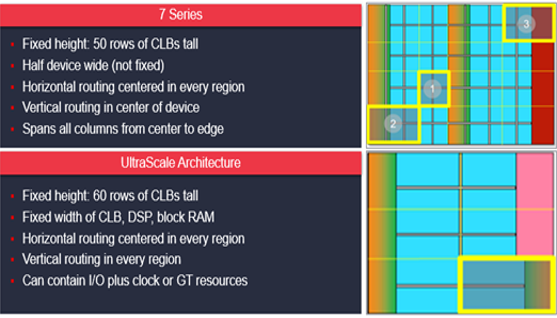

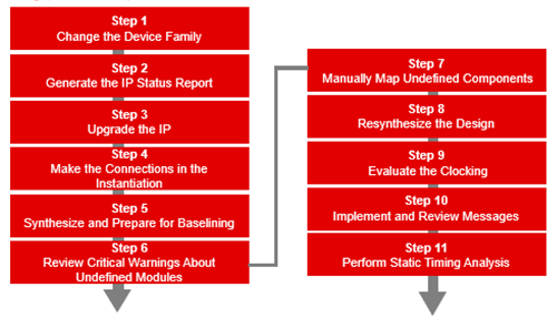

Objective: Migrate an existing 7 series design to the UltraScale architecture.

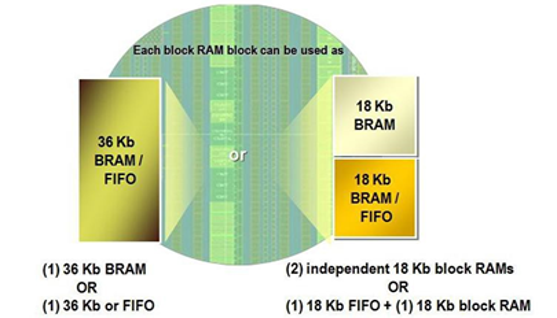

Objective: Review the block RAM resources in the UltraScale architecture.

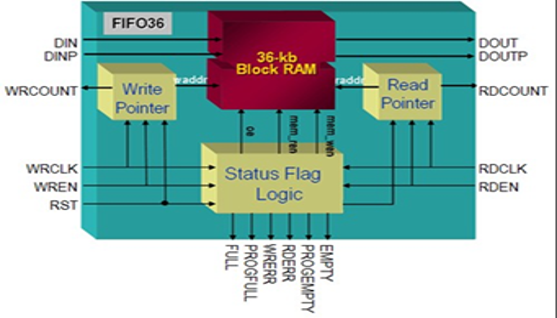

Objective: Review the FIFO resources in the UltraScale architecture.

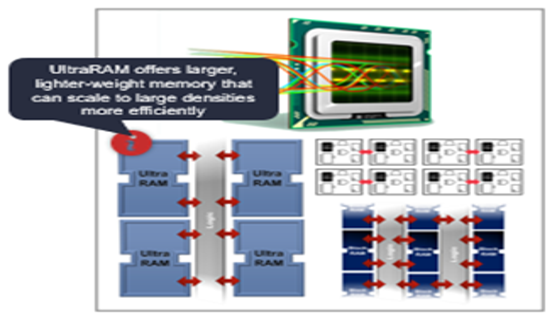

Objective: Use UltraRAM for a design requiring a larger memory size than block RAM.

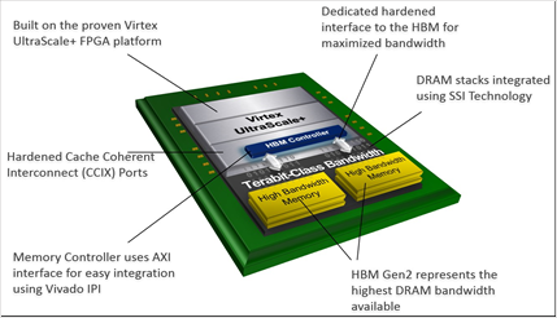

Objective: Use high bandwidth memory (HBM) for applications requiring high bandwidth.

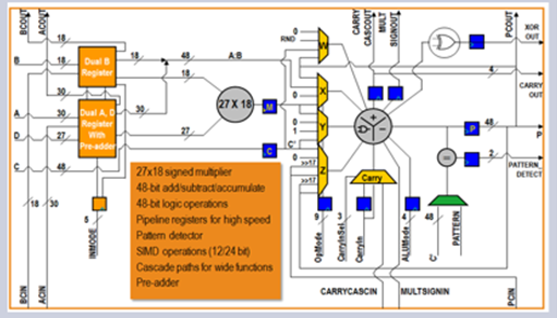

Objective: Review the DSP resources in the UltraScale architecture.

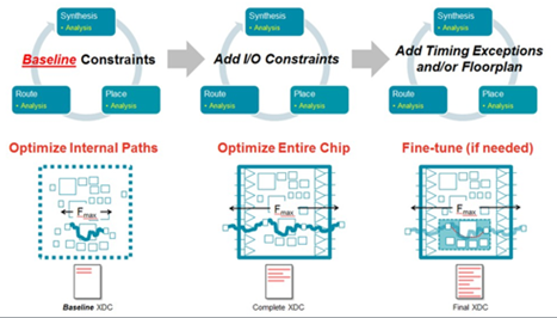

Objective: List the Xilinx software recommendations for design migrations from 7 series to the UltraScale architecture.

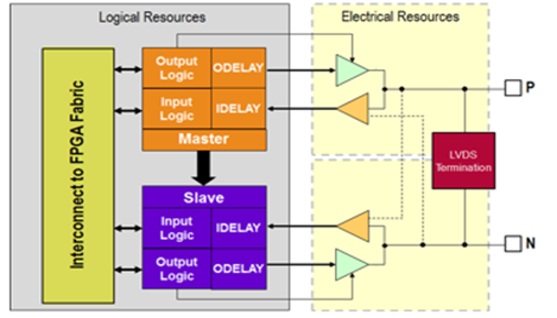

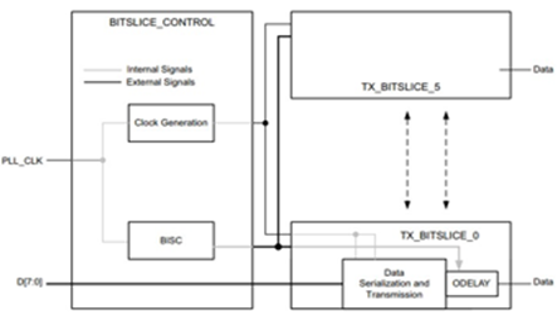

Objective: Review the I/O resources in the UltraScale architecture.

Objective: Implement a high-performance, source-synchronous interface using I/O resources in Component mode for the UltraScale architecture.

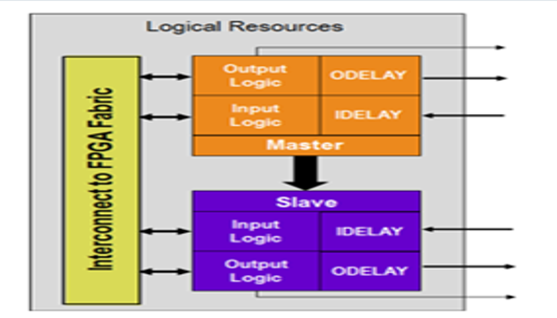

Objective: Implement a high-performance, source-synchronous interface using I/O resources in Native mode for the UltraScale

architecture.

Objective: Review the migration methodology recommended by Xilinx for design migrations.

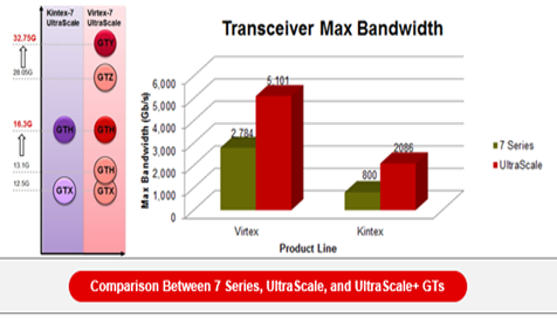

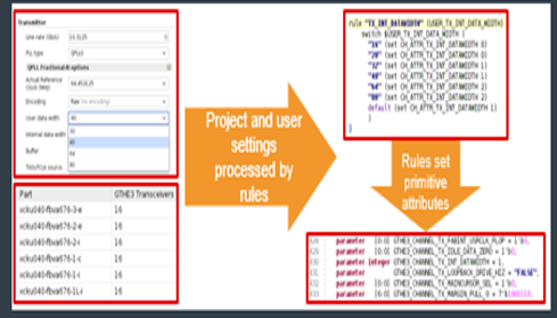

Objective: Review the enhanced features of the transceivers in the UltraScale architecture.

Objective: Use the Transceivers Wizard to build a design that uses a single serial transceiver and observe the created file structures.

Objective: Identify the enhancements made to the UltraScale architecture in the UltraScale+ architecture families.