TechSource Systems is MathWorks Authorised Reseller and Training Partner

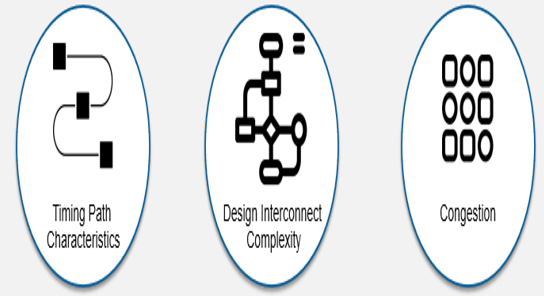

Learn the fundamental of the static timing analysis (STA), follow by how to achieve design closure more efficiently and tackle hard timing challenges.

This three-day provides experience with:

Hands-on Project on the last day allows you to test your knowledge and apply your skills immediately. No documentation, no labs instructions, you will face the real challenge to do a full FPGA design flow project with the guidance of our instructor

Software and hardware developers, system architects, and anyone who wants to learn about design closure techniques.

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

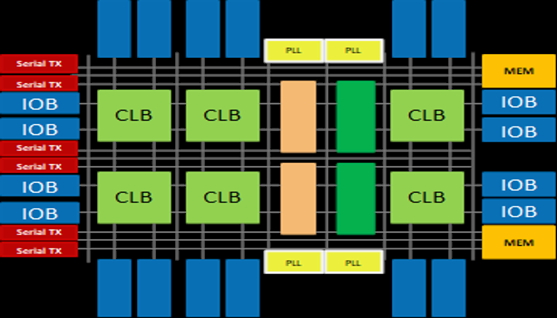

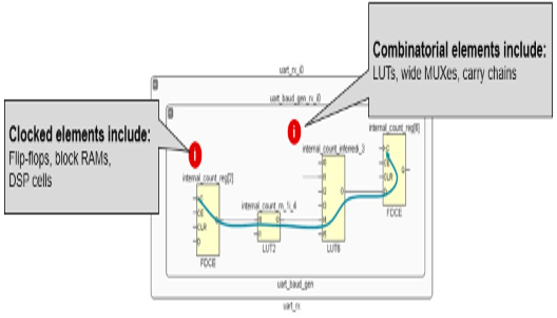

Objective: Overview of FPGA architecture, SSI technology, and SoC device architecture.

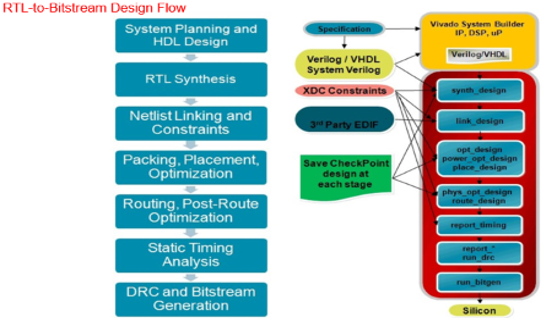

Objective: Introduces the Vivado design flows: the project flow and non-project batch flow.

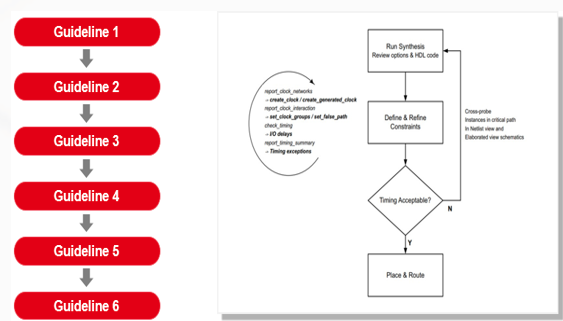

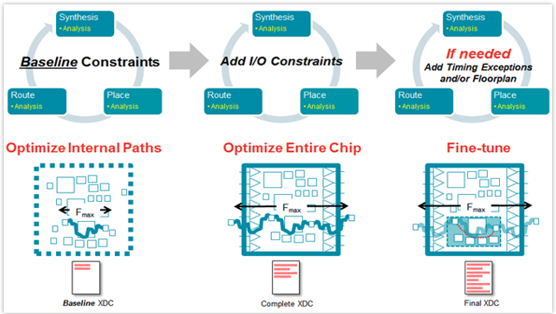

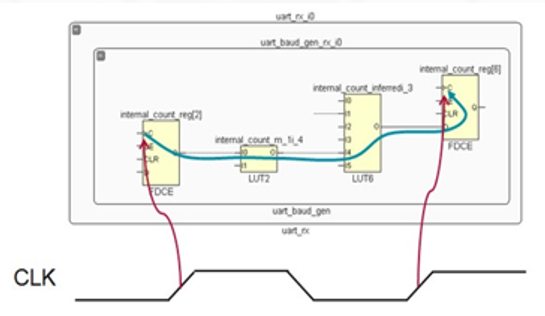

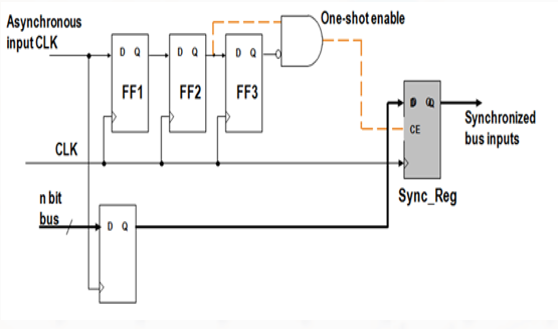

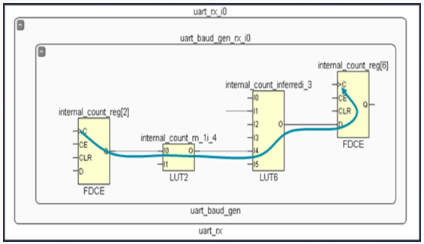

Objective: Apply clock constraints and perform timing analysis.

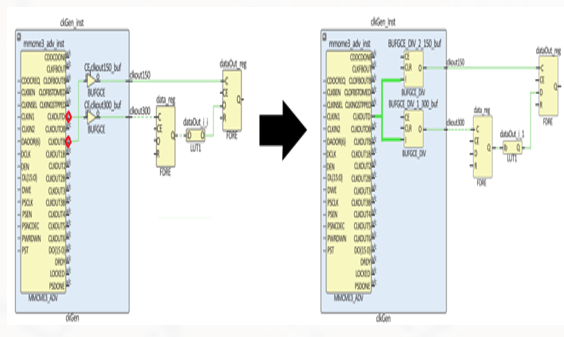

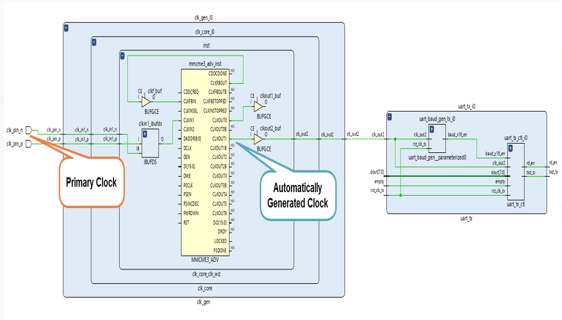

Objective: Use the report clock networks report to determine if there are any generated clocks in a design.

Objective: Use the Timing Constraints Wizard to apply missing timing constraints in a design.

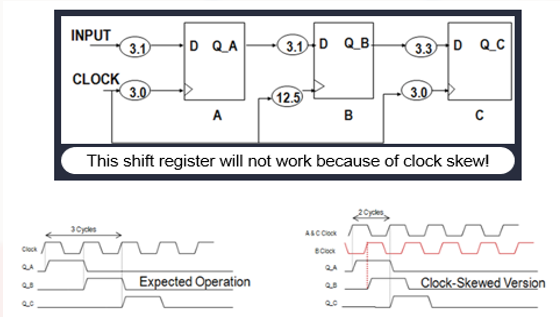

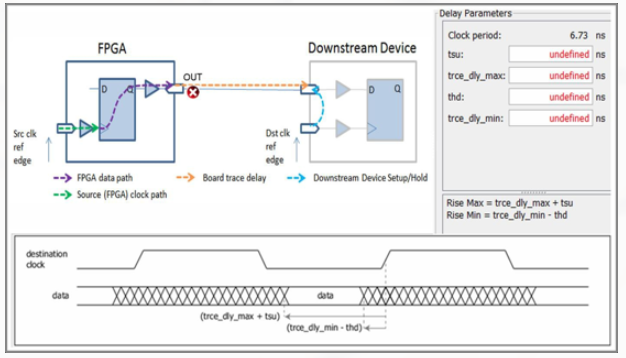

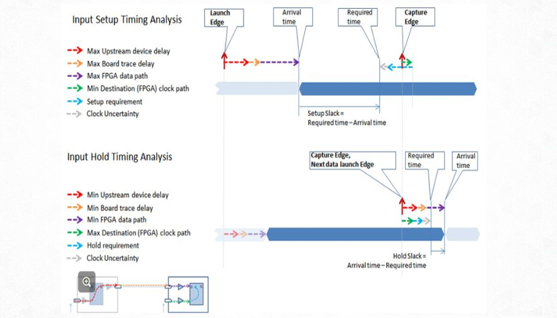

Objective: Describes the basics of clock gating and static timing analysis.

Objective: Reviews setup and hold timing calculations.