TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn how to achieve design closure more efficiently and productively by using the three pillars of design closure (functional closure, timing closure, and power closure). Also learn how to solve functional behavior, timing, and power simultaneously to achieve faster time-to-market results.

The emphasis of this two days course is on:

Software and hardware developers, system architects, and anyone who wants to learn about design closure techniques related to functional, timing, and power closure

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

Introduction to Design Closure

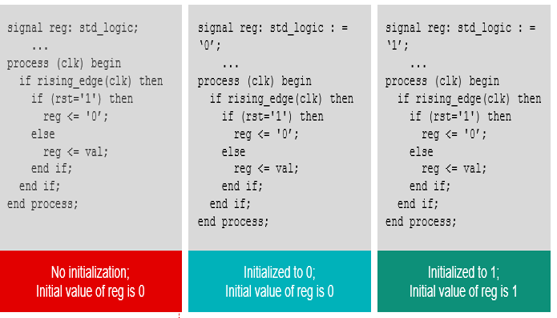

HDL Coding Technique

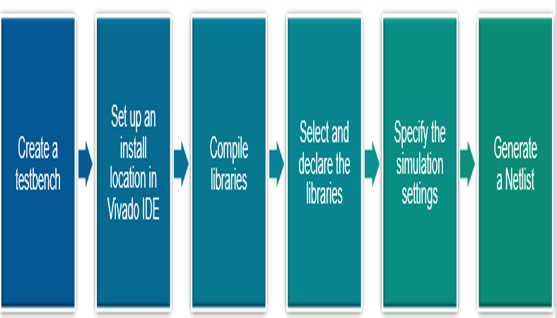

Creating a Test Bench

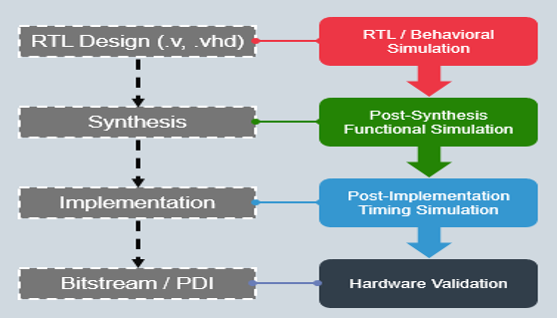

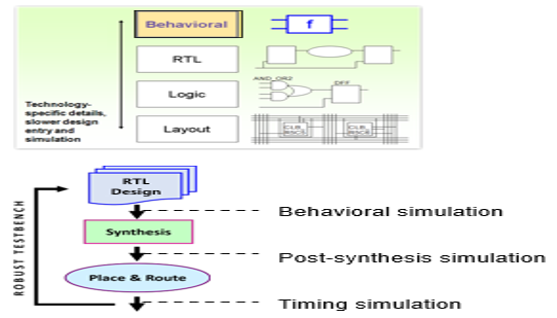

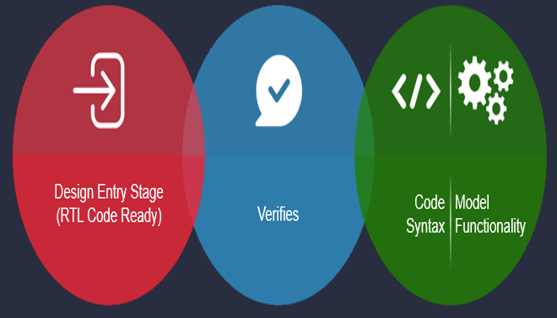

Behavioral Simulation

Timing Simulation

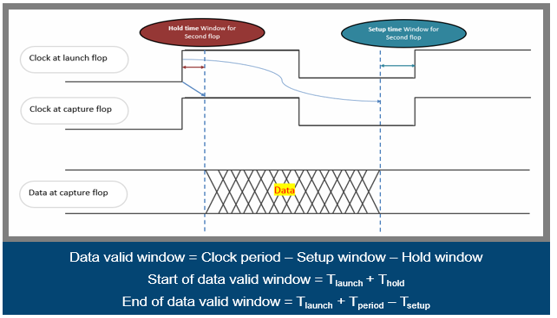

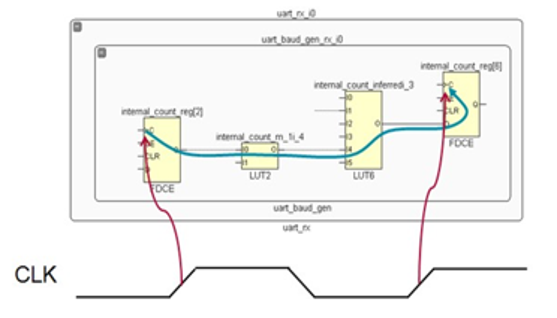

Introduction to Clocking and Static Timing Analysis (STA)

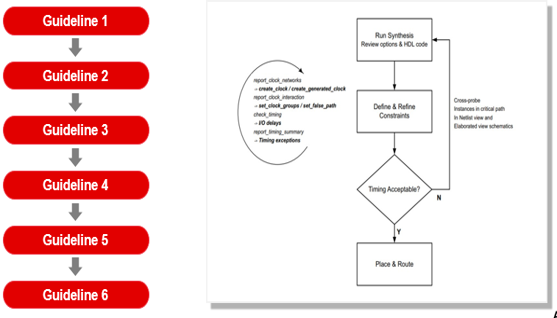

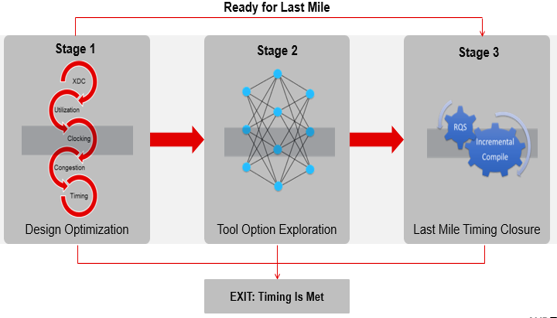

Introduction to UltraFast Design Methodology Timing Closure

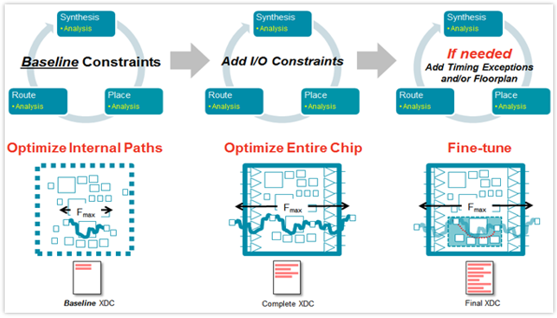

Baselining

Setup and Hold Violation Analysis

Reducing Logic Delay

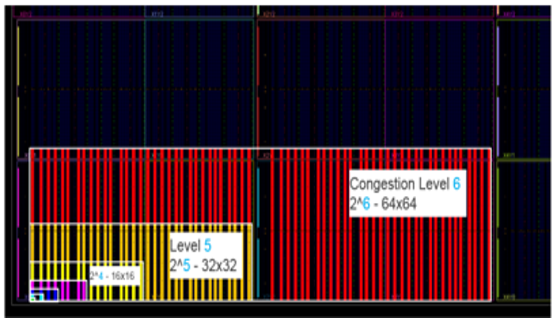

Reducing Net Delay

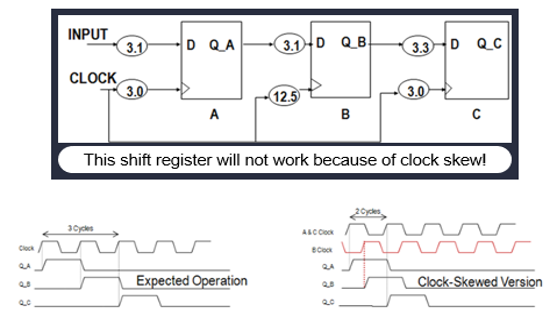

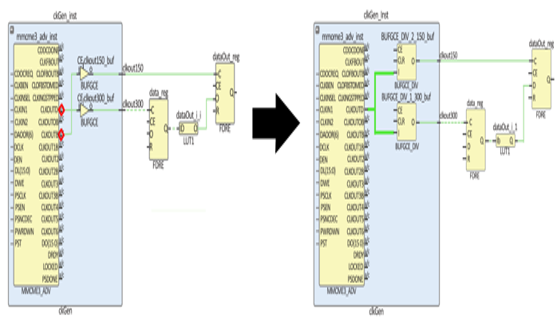

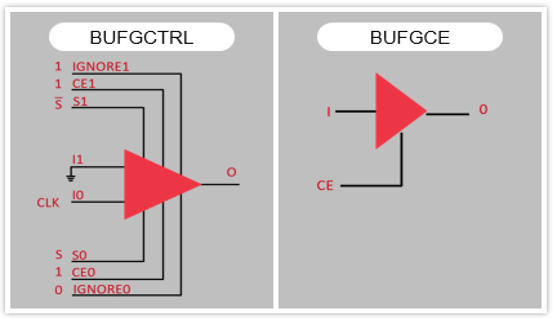

Improving Clock Skew

Improving Clock Uncertainty

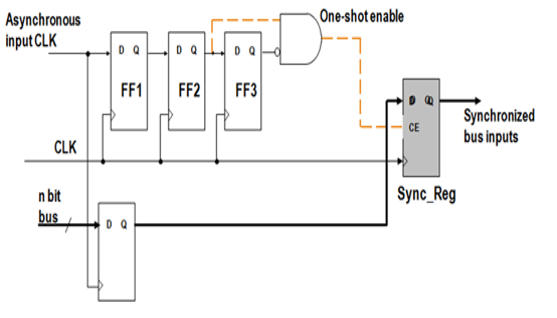

Clock Domain Crossing (CDC) and Synchronization Circuits

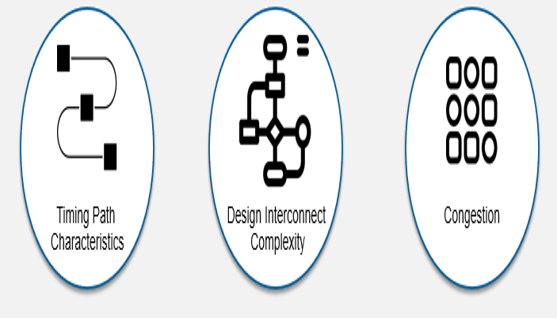

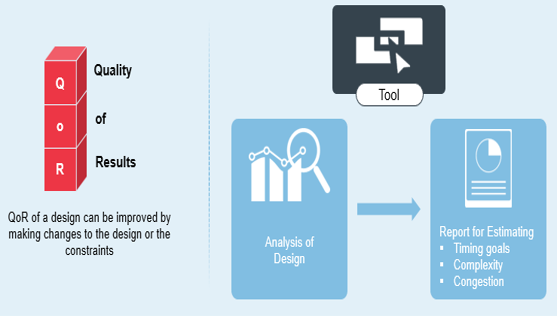

QoR Reports Overview

Intelligent Design Runs (IDR)

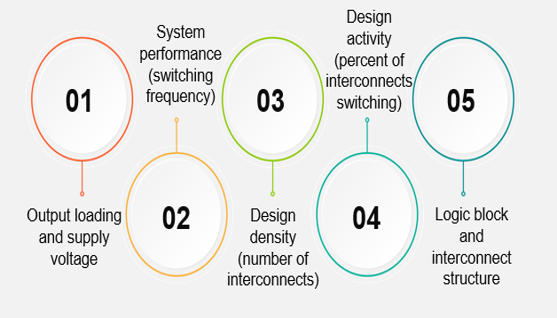

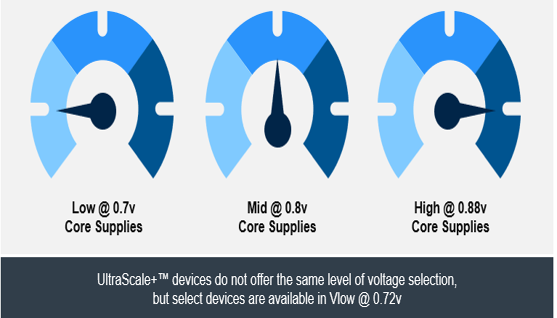

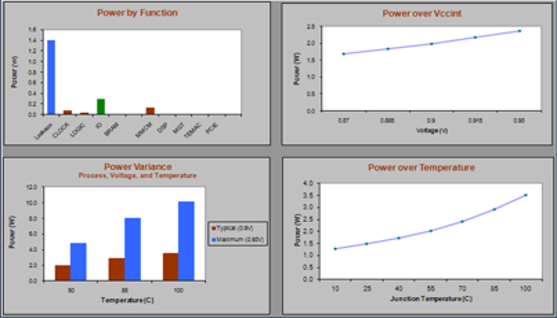

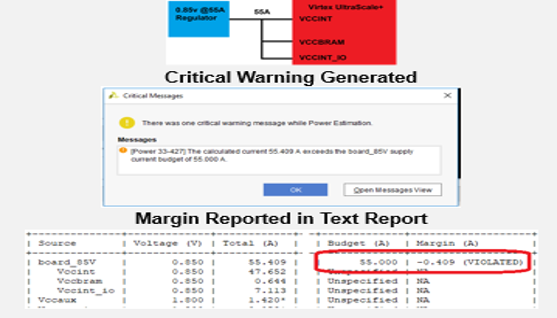

Understanding Design Power for Better Time to Market

Xilinx Power Estimator Spreadsheet

Versal ACAP: Power and Thermal Solutions

Design Power Constraints

Power Management Techniques

Power Analysis and Optimization Using the Vivado Design Suite