TechSource Systems is MathWorks Authorised Reseller and Training Partner

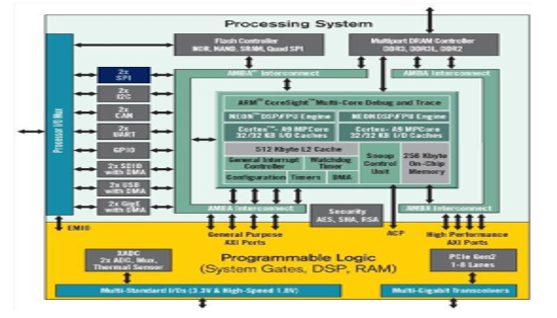

Software design engineers will learn how to make full use of the components available in the Zynq® System on a Chip (SoC) processing system (PS).

The emphasis of this one day course is on:

Software design engineers interested in fully using the Zynq extensible processing platform

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

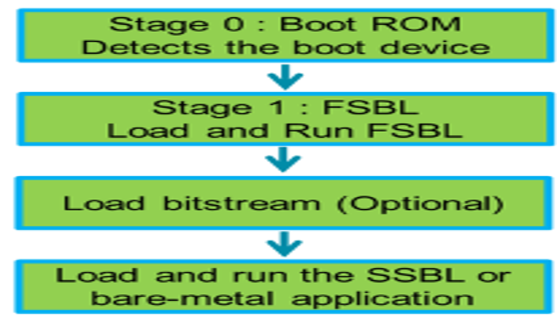

Objective: Introduces the main points to how booting a processor is handled in Zynq devices and MicroBlaze processors.

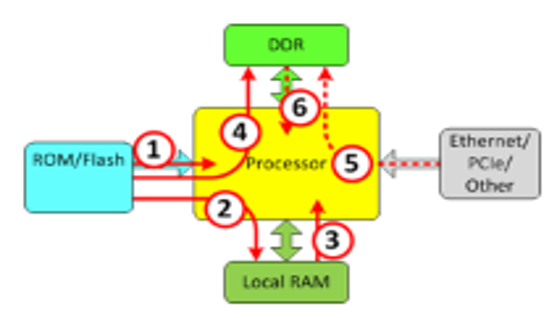

Objective: Introduces the main points of the memories that can be booted or executed from.

Objective: Provides a low-level view of the booting process.

Objective: Introduces the concepts behind a single-core boot, a dual-core boot, and symmetric or asymmetric processing.

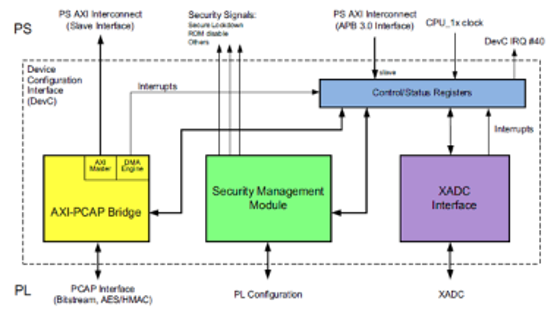

Objective: Introduces the concepts behind configuring the PL at boot.

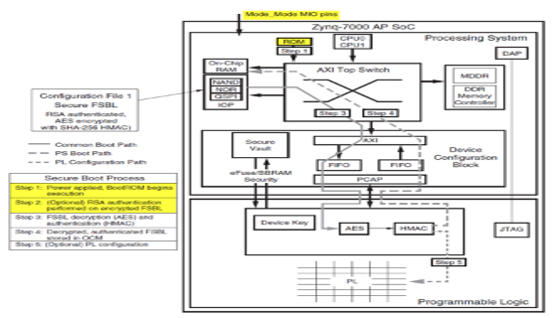

Objective: Introduces the concepts behind secure booting.

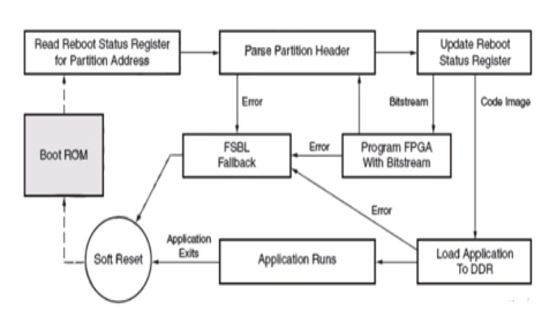

Objective: Introduces the First Stage Boot Loader (FSBL).

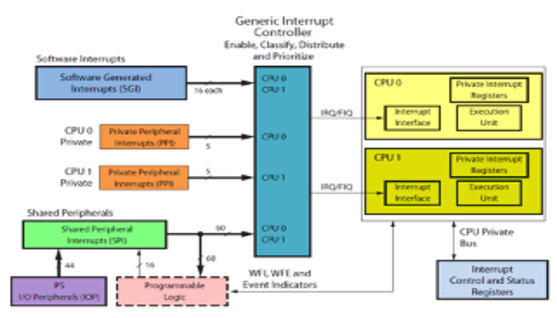

Objective: Introduces the general interrupt controller (GIC), its features, and some examples of its use.

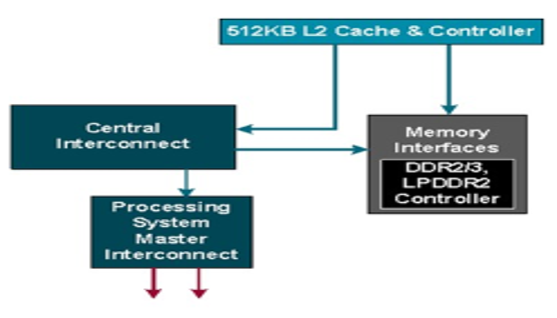

Objective: Introduces the concepts behind processing caching and the System-Level Control Register.

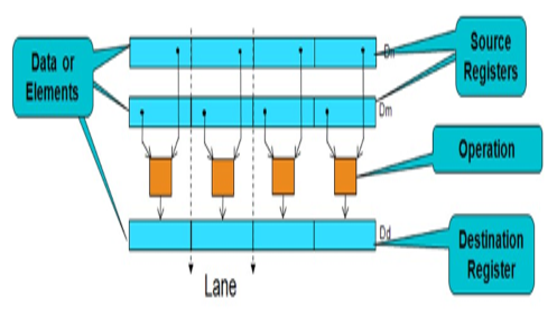

Objective: Introduces the concepts behind the NEON co-processor.

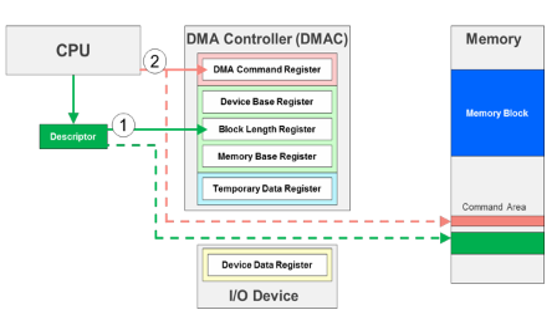

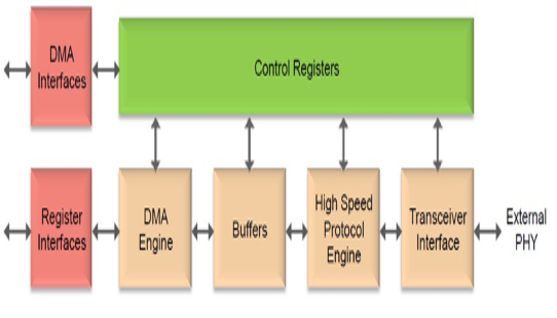

Objective: Introduces the direct memory access controller.

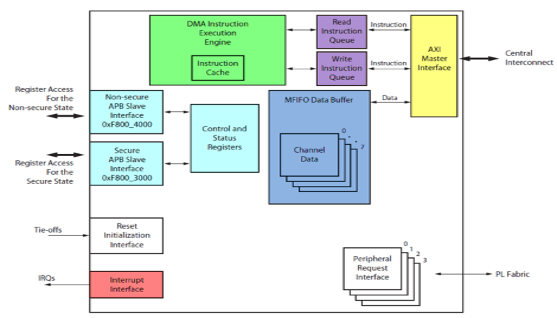

Objective: Introduces the DMA block design and the DMA interrupts.

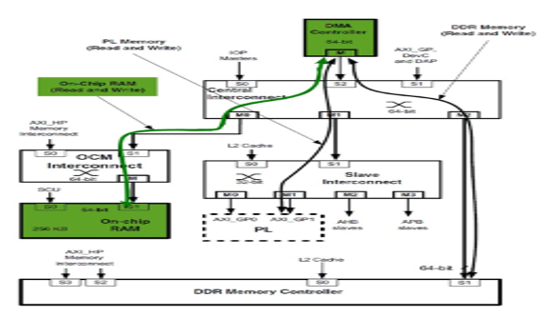

Objective: Introduces the concepts behind DMA reading and writing.

Objective: Introduces the Gigabit Ethernet high-speed peripheral.

Objective: Introduces the USB high-speed peripheral.

Objective: Introduces the low-speed peripherals in the Zynq SoC.

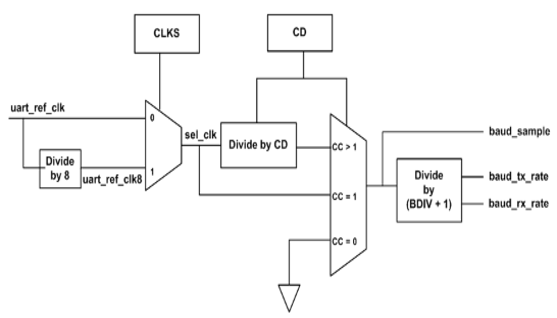

Objective: Introduces the UART low-speed peripheral.

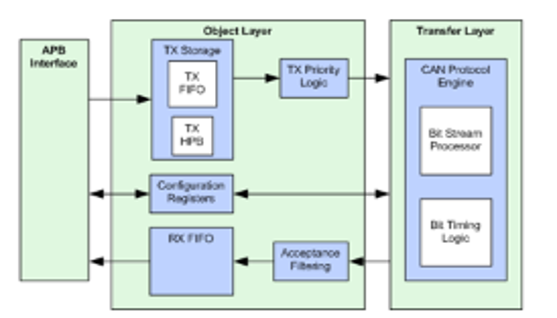

Objective: Introduces the CAN low-speed peripheral.

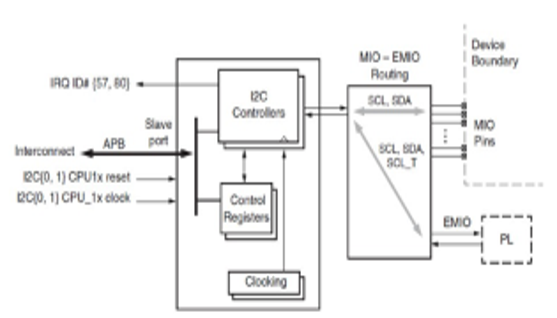

Objective: Introduces the I2C low-speed peripheral.

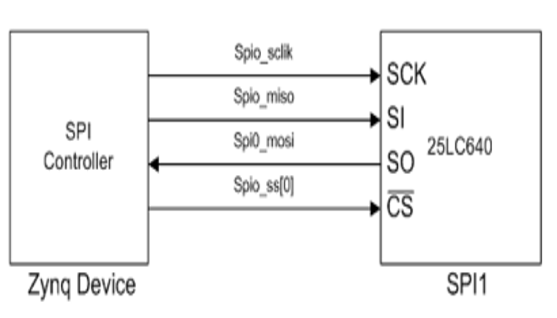

Objective: Introduces the SPI low-speed peripheral.

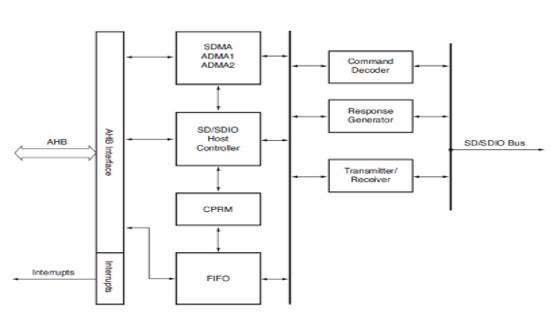

Objective: Introduces the SD/SDIO low-speed peripheral.