TechSource Systems is MathWorks Authorised Reseller and Training Partner

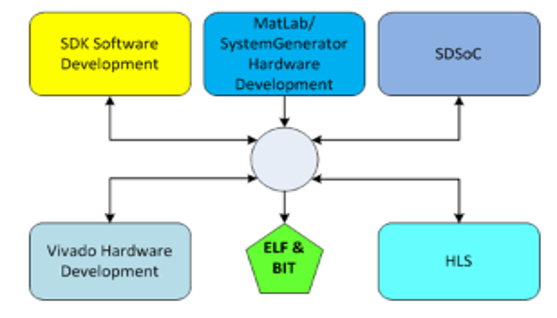

Learn how to use advanced components of embedded systems design for architecting a complex system in the Zynq System on a Chip (SoC) or MicroBlaze™ soft processor

The emphasis of this two days course is on:

Hardware, firmware, and system design engineers who are interested in Xilinx embedded systems development flow

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

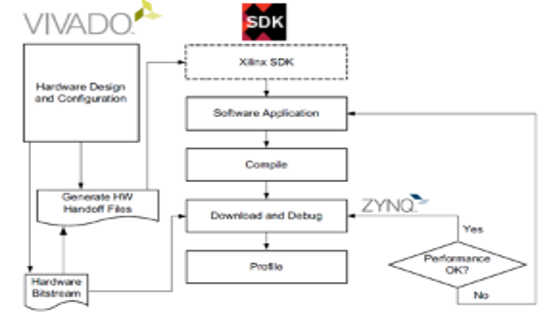

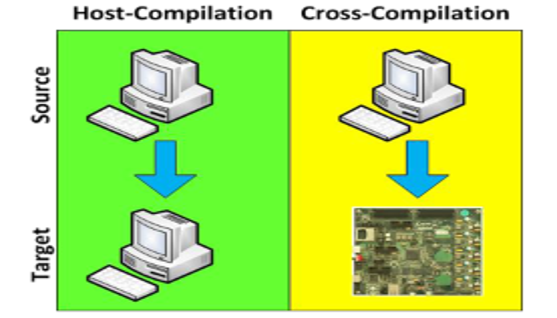

Objective: Provides an overview of embedded hardware development.

Objective: Illustrates how design information generated during the hardware development process is moved into the SDK tool realm.

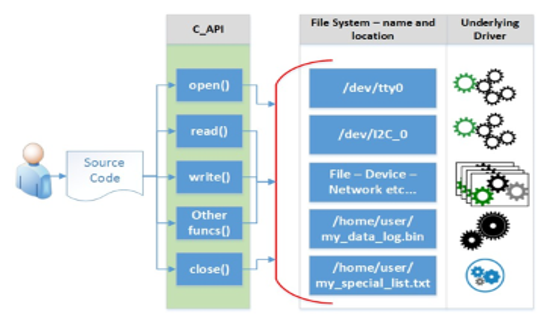

Objective: Provides a thorough understanding of how the integrated design environment works, including how the compiler and linker behave, basics of makefiles, DMA usage, and variable scope.

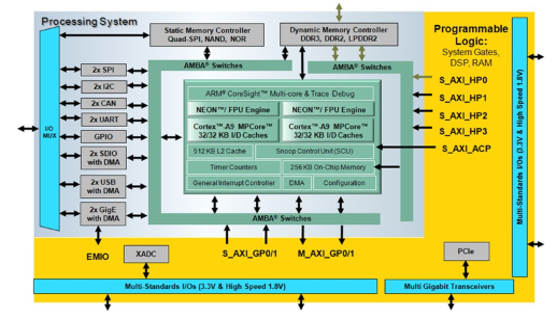

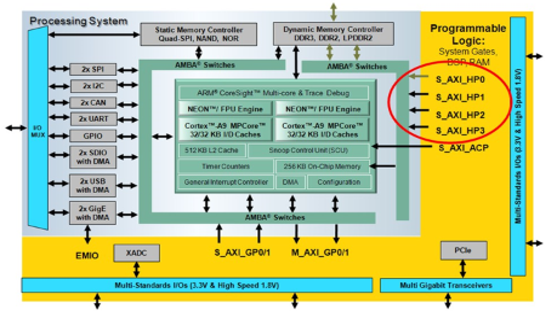

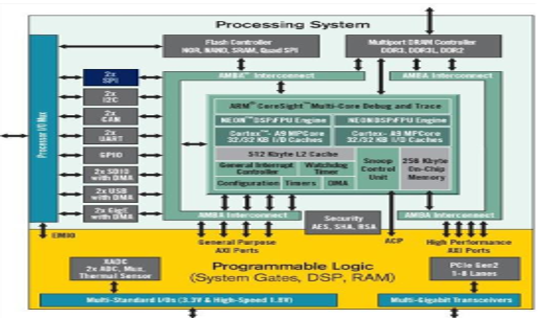

Objective: Overview of the Zynq7000 SoC architecture.

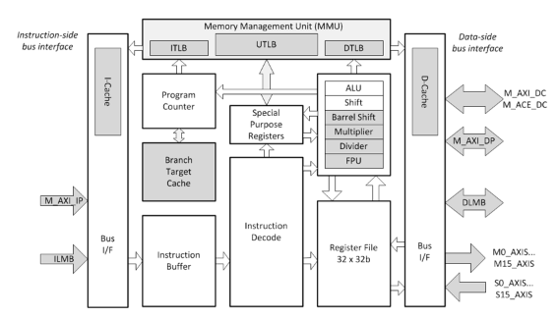

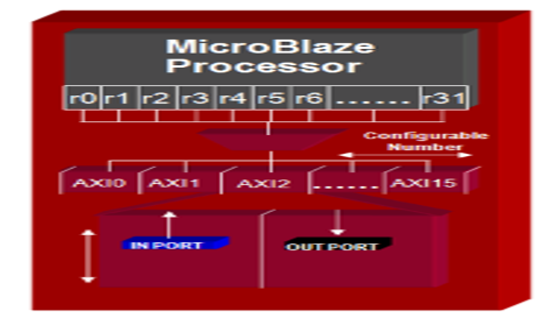

Objective: Overview of the MicroBlaze microprocessor architecture.

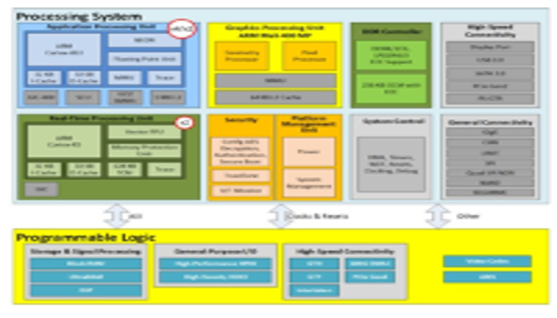

Objective: Overview of the Zynq UltraScale+ MPSoC architecture.

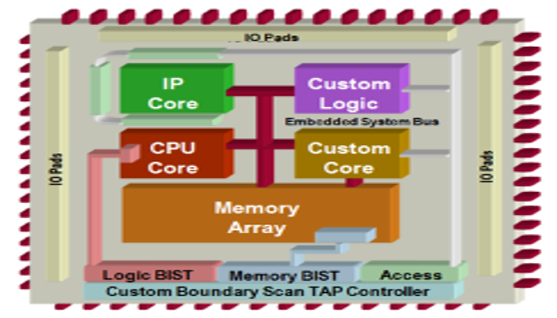

Introduces the need and offers a solution for in-chip testing of hardware designs.

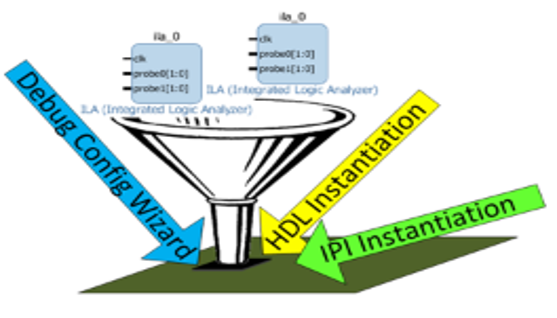

Objective: Reviews the process of marking nets to show which signals should be monitored without having to explicitly instantiate ILA cores.

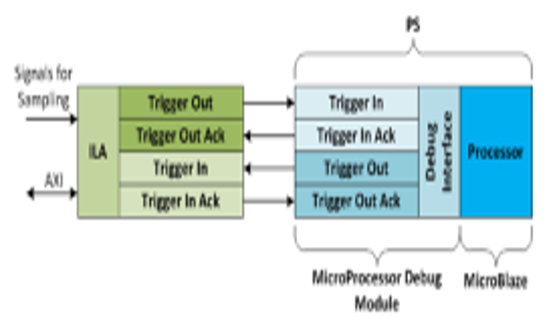

Objective: Describes how to enable events in hardware to pause the software execution and breakpoints in software to cause an ILA trigger.

Objective: Provides a brief overview of the different types of memory available, as well as when one type of memory would be selected over another.

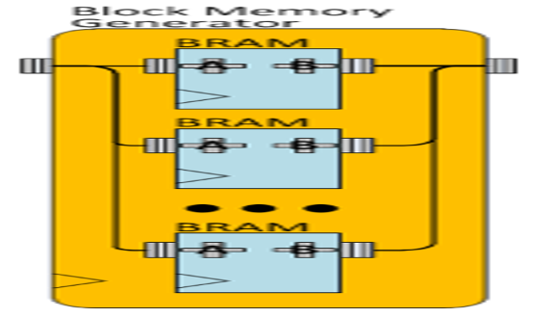

Objective: – Introduces two versions of block RAM controllers and how and why they are needed.

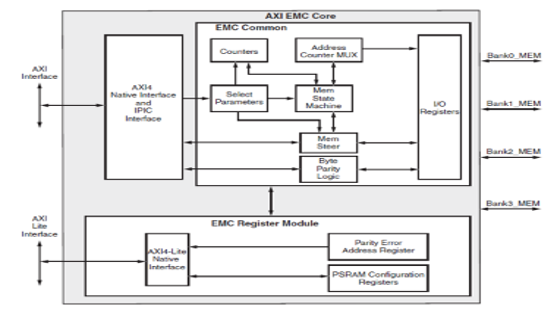

Objective: Discusses static memory controllers in general and the SMC implementation in the Zynq-7000 family of devices.

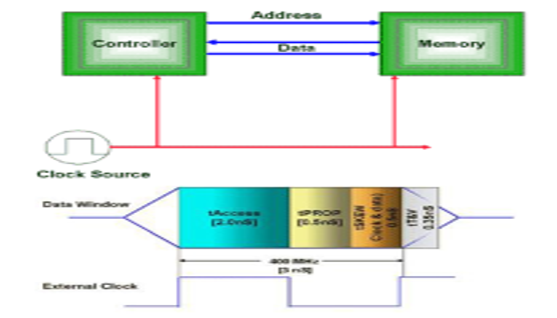

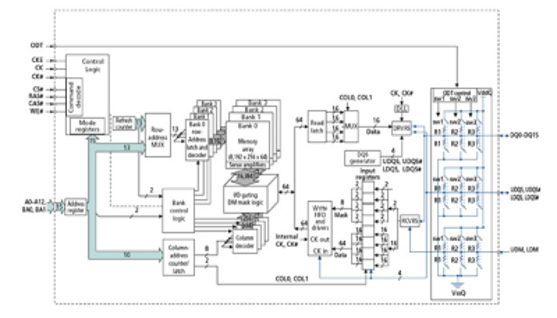

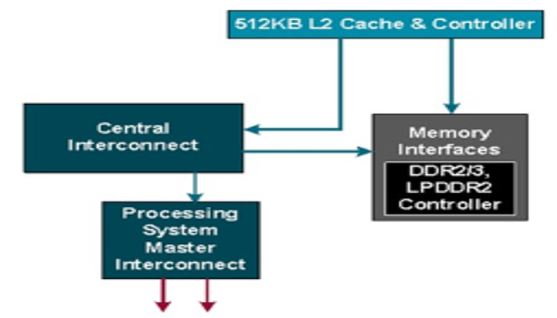

Objective: Provides additional details regarding how DDRx memory interfaces with a controller.

Objective: Covers how the DMC is implemented as well as many of its key behaviors.

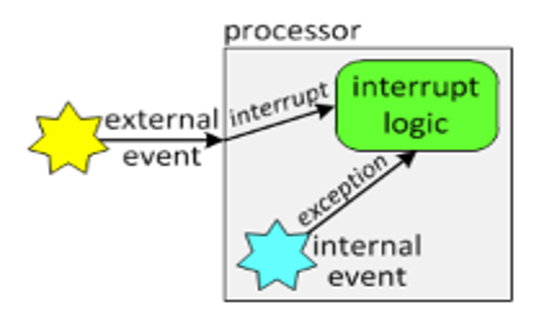

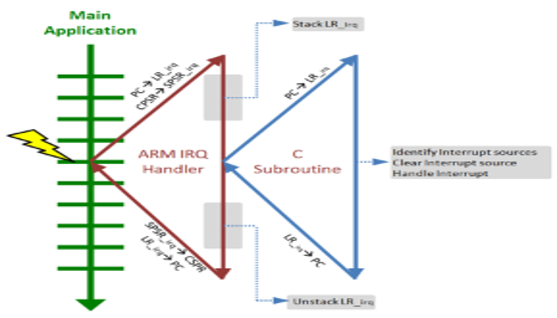

Objective: Introduces the concept of interrupts, basic terminology, and generic implementation.

Objective: – Presents the details of how the Zynq-7000 platform uses interrupts from both a hardware and software perspective.

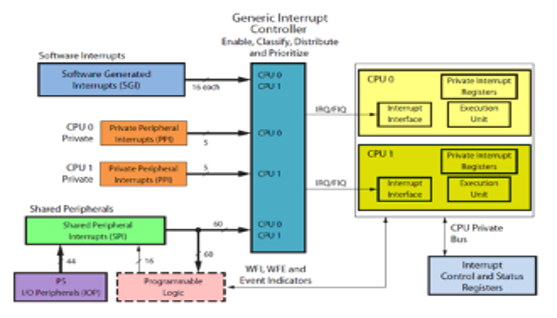

Objective: Introduces the general interrupt controller (GIC), its features, and some examples of its use.

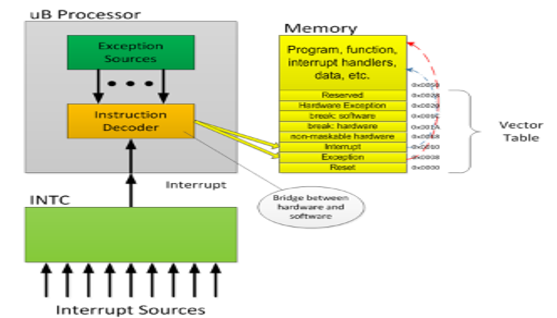

Objective: Describes how interrupts are handled within the MicroBlaze processor system from a hardware perspective.

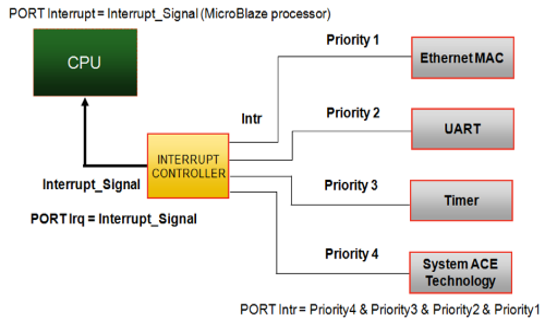

Objective: Introduces the AXI Interrupt Controller, which augments the MicroBlaze processor’s interrupt capabilities by managing multiple interrupt sources.

Objective: – Provides the context and background for the the streaming configuration of the AXI protocol.

Objective: Describes and illustrates how data streaming is performed using the MicroBlaze processor.

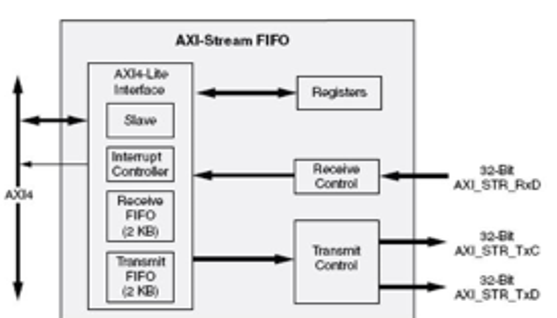

Objective: Introduces the AXI Streaming FIFO and its capabilities.

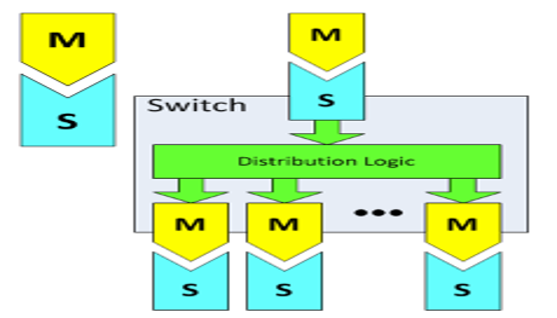

Objective: Focuses on the relationships between different types of AXI interfaces and how they can be connected to form hierarchies.

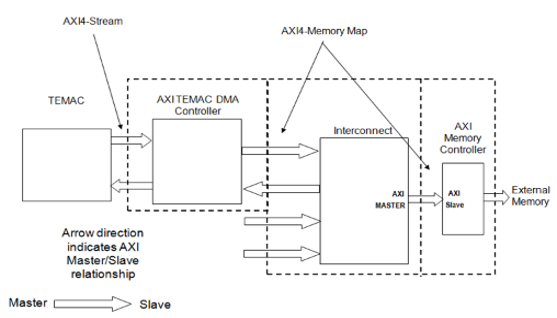

Objective: Introduces various IP that supports DMA and DMA-like functionality.

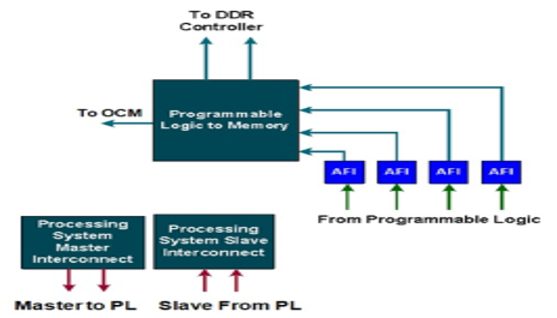

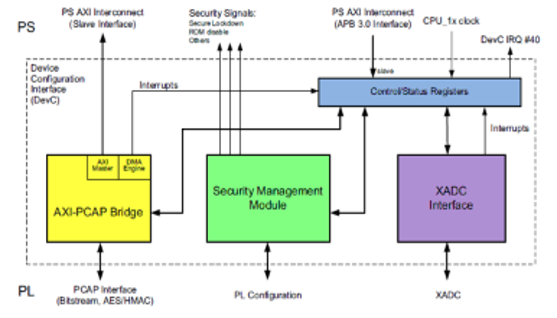

Objective: Discusses the various connection points between the PS and PL.

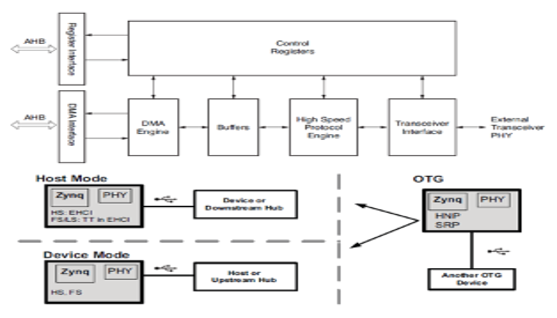

Objective: Introduces the USB high-speed peripheral.

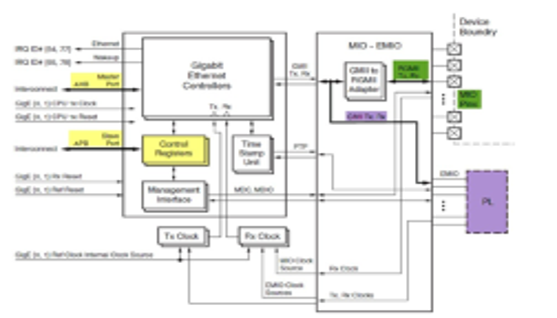

Objective: Introduces the Gigabit Ethernet high-speed peripheral.

Objective: Introduces the low-speed peripherals in the Zynq SoC.

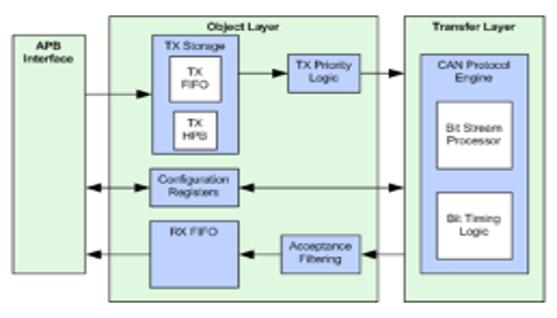

Objective: Introduces the CAN low-speed peripheral.

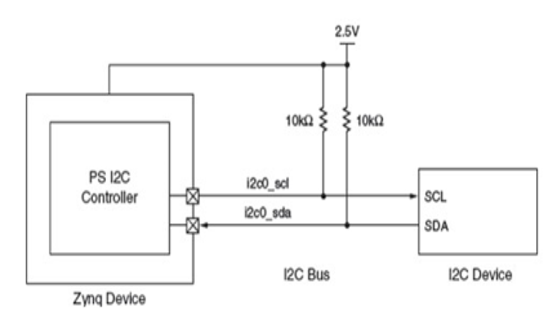

Objective: Introduces the I2C low-speed peripheral.

Objective: Introduces the SD/SDIO low-speed peripheral.

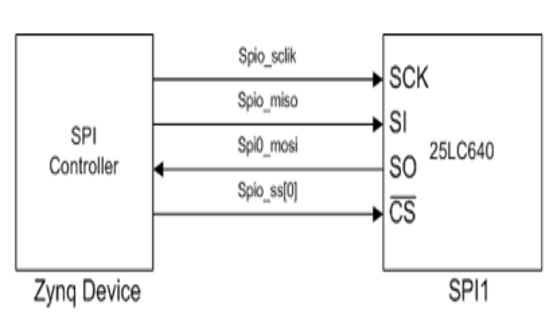

Objective: Introduces the SPI low-speed peripheral.

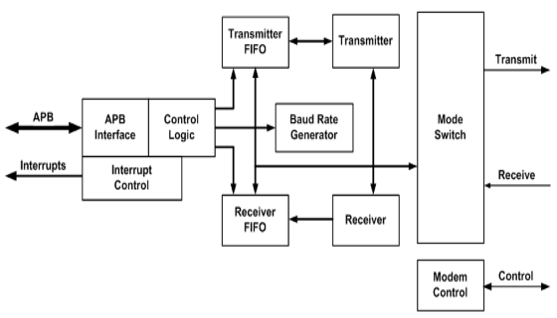

Objective: Introduces the UART low-speed

peripheral.

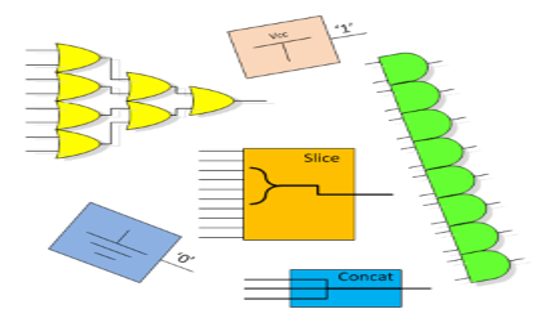

Objective: Covers the IP that provides basic logic support within the block design.

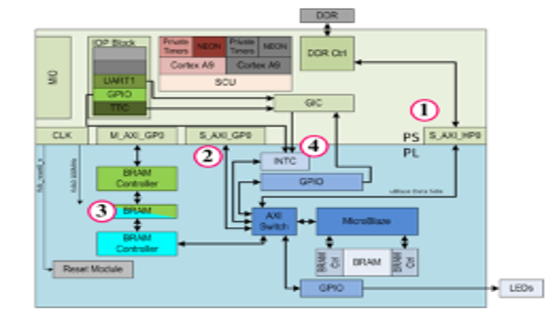

Objective: Illustrates from the hardware design perspective how a master in the PL can leverage resources within the PS.

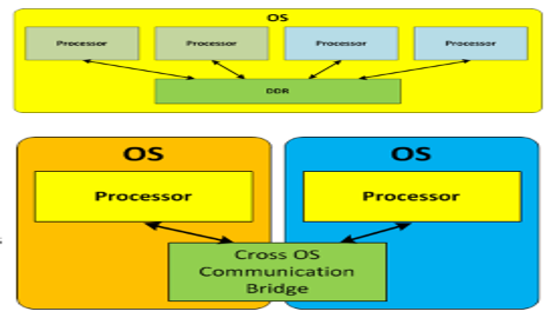

Objective: Addresses some of the mechanisms that a designer can leverage to support cross processor communications.

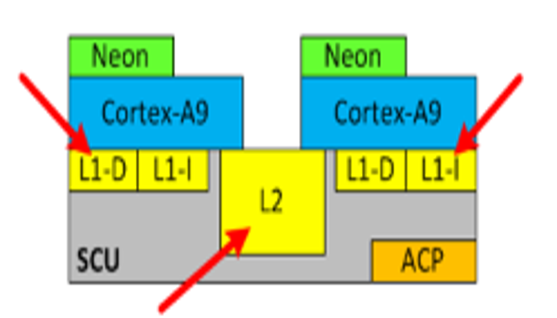

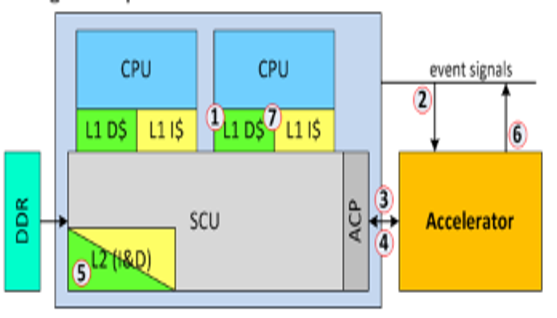

Objective: – Introduces the concept of caching and describes how this technique is implemented using the Xilinx processor systems.

Objective: Introduces the concepts behind processing caching and the System-Level Control Register.

Objective: Describes the purpose and general behavior of the accelerator coherency port (ACP).

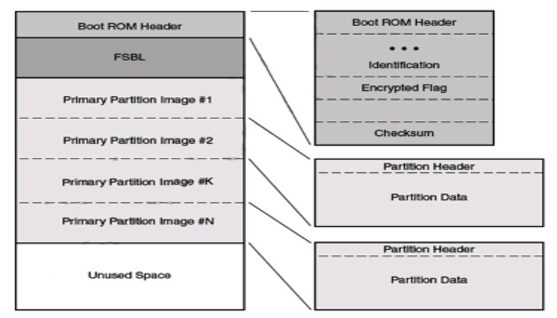

Objective: Provides a low-level view of the booting process.

Objective: Introduces the concepts behind configuring the PL at boot.

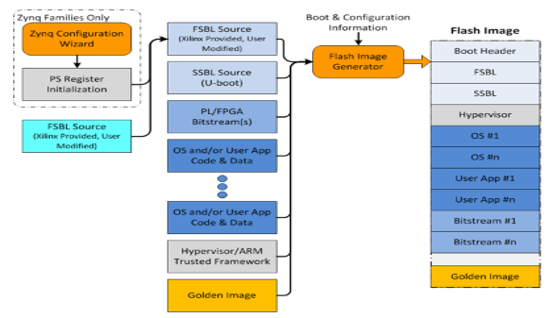

Objective: Introduces the Flash Image Generator tool, which is used to collect up a variety of files and order them properly in the Flash so that the FSBL can correctly read them.

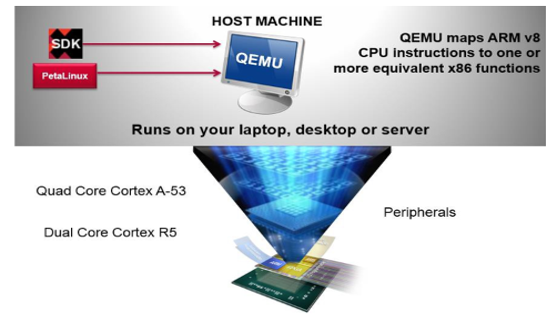

Objective: Introduction to the Quick Emulator, which is the tool used to run software for the Zynq device when hardware is not available.