TechSource Systems is MathWorks Authorised Reseller and Training Partner

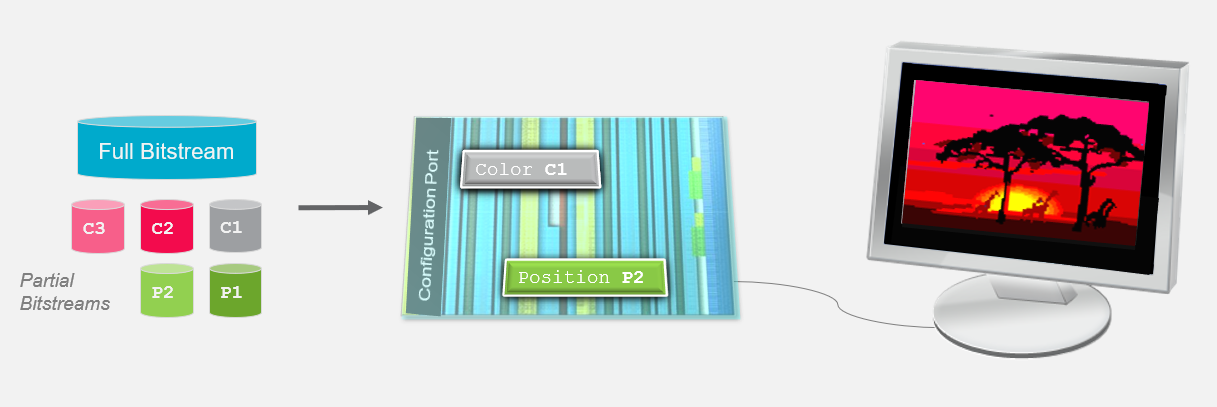

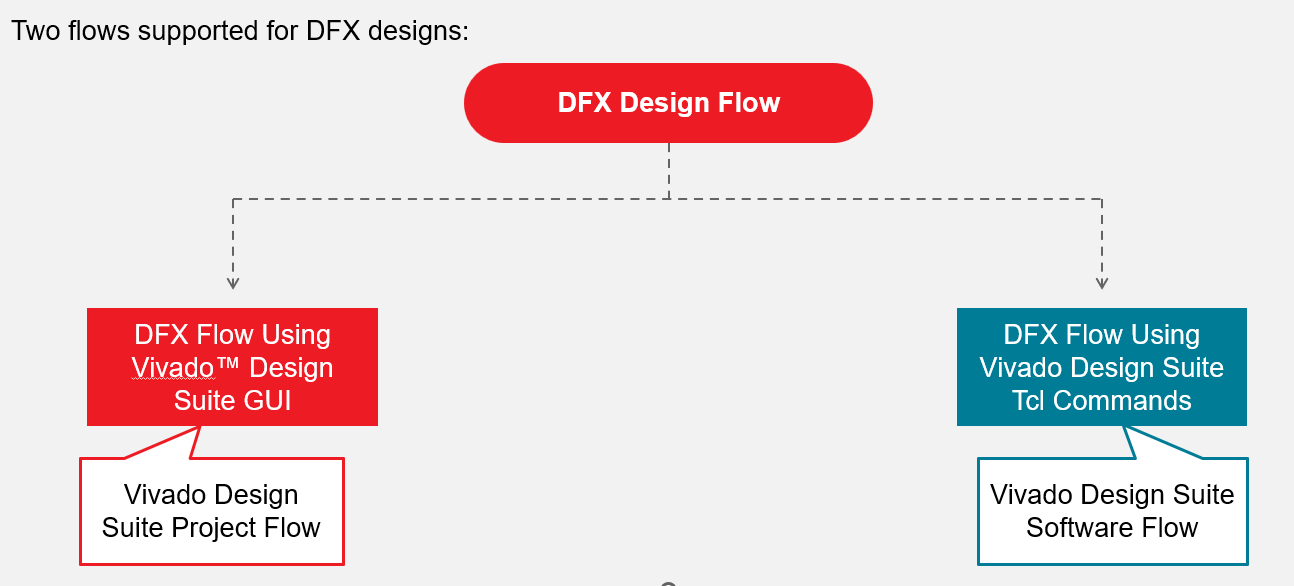

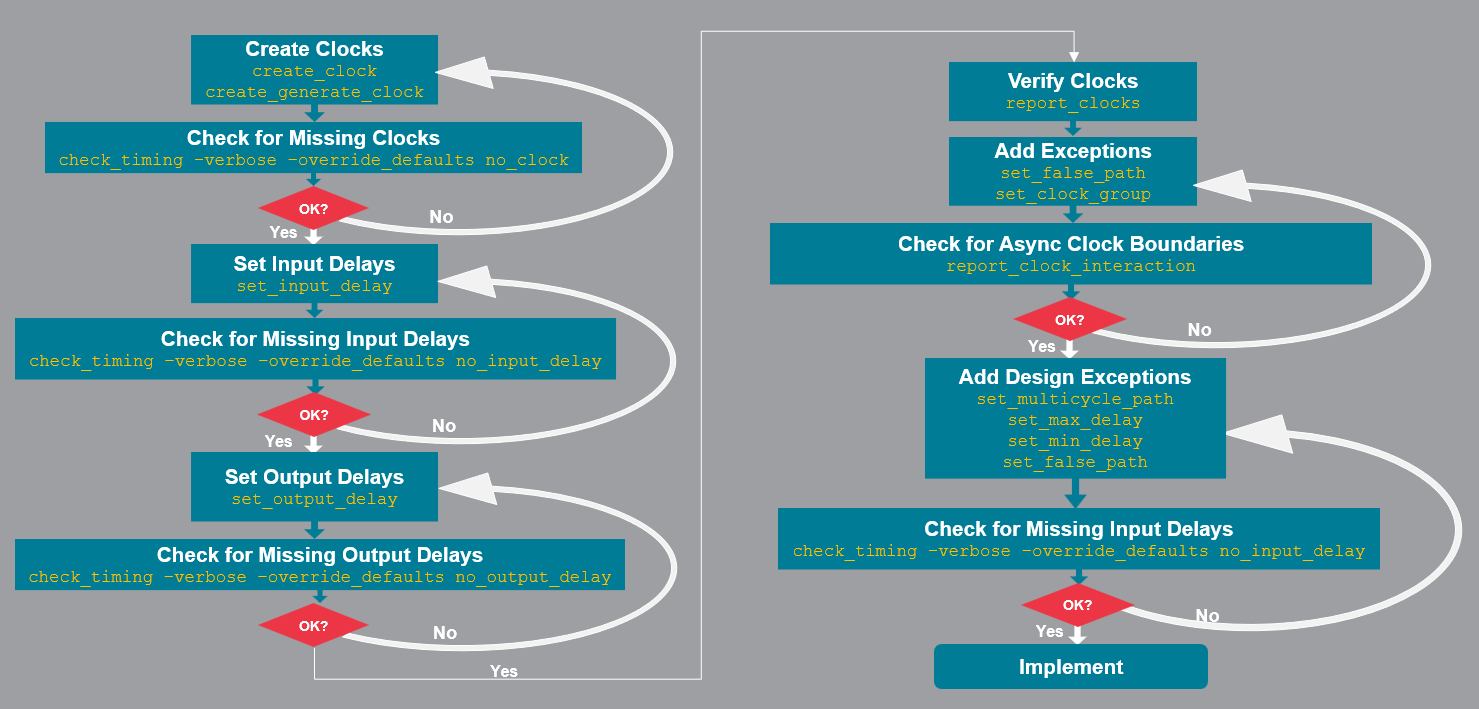

Learn how to construct, implement, and download a Dynamic Function eXchange (DFX) FPGA design using the Vivado™ Design Suite. This course covers both the tool flow and mechanics of successfully creating a DFX design.

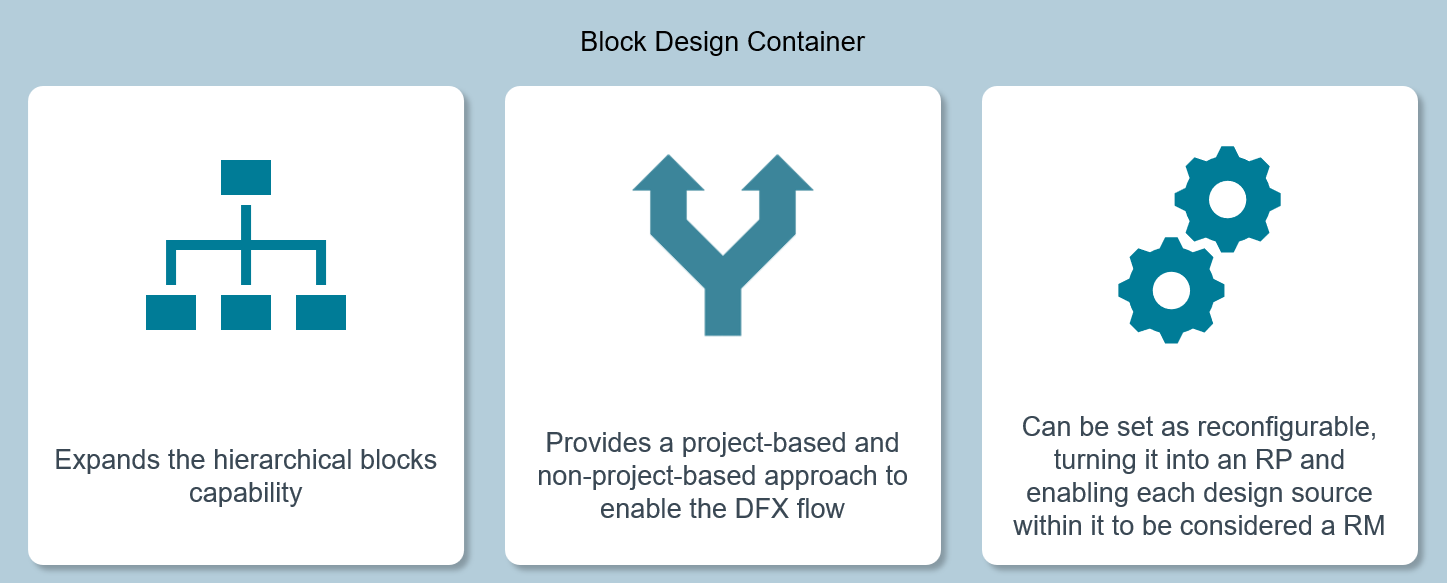

This two-day provides experience with:

Hands-on Project allows you to test your knowledge and apply your skills immediately. No documentation, no labs instructions, you will face the real challenge to do a full FPGA design flow project with the guidance of our instructor

Digital designers who have a working knowledge of HDL (VHDL or Verilog) and digital design and who want to implement Dynamic Function eXchange techniques.

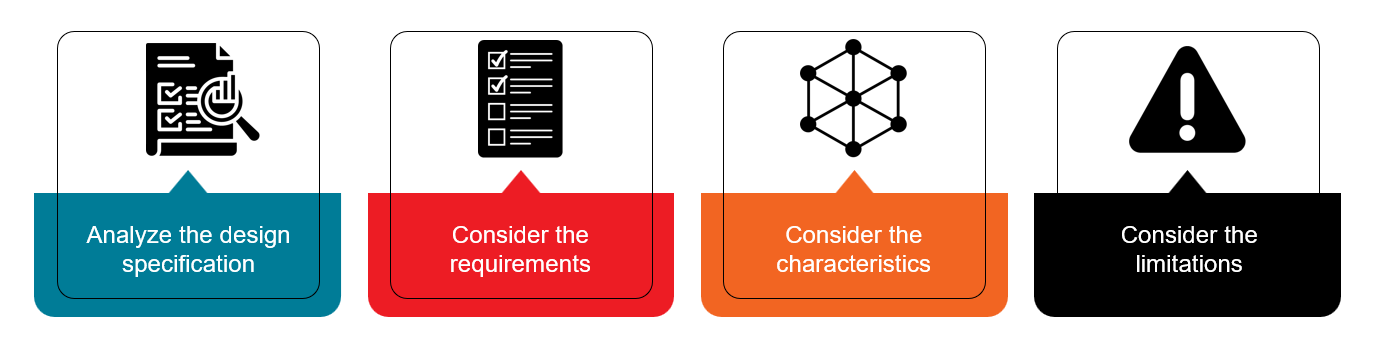

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner