TechSource Systems is MathWorks Authorised Reseller and Training Partner

Learn how to implement a Xilinx PCI Express® core in custom

applications to improve time to market with the PCIe® core design

This two-day course provides you with the skill and knowledge on how to implement a Xilinx PCI Express® core in custom

applications to improve time to market with the PCIe® core design.

The focus is on:

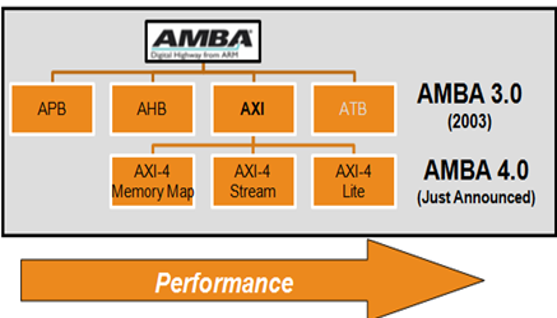

This course also focuses on the AXI Streaming interconnect.

What’s New for 2020.2

After completing this comprehensive training, you will have the necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

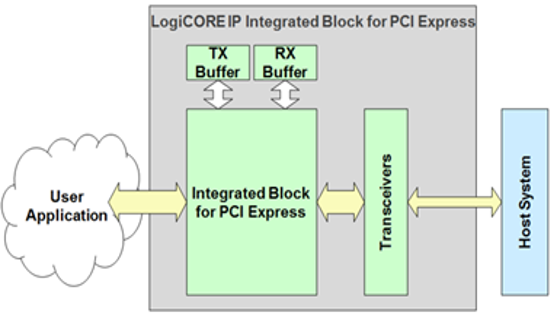

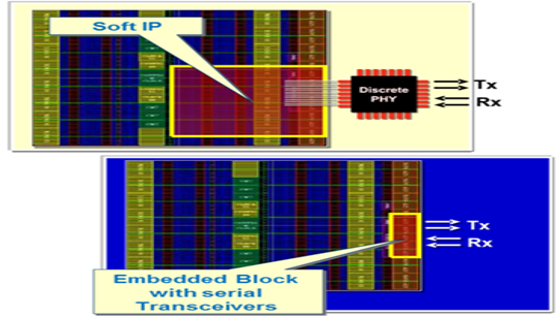

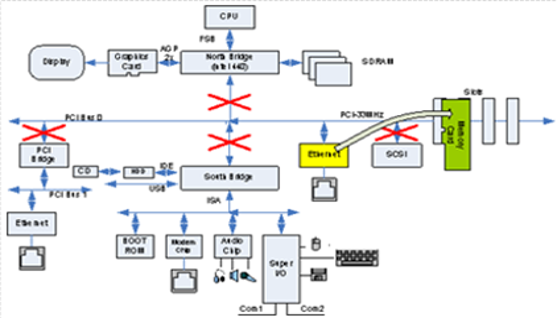

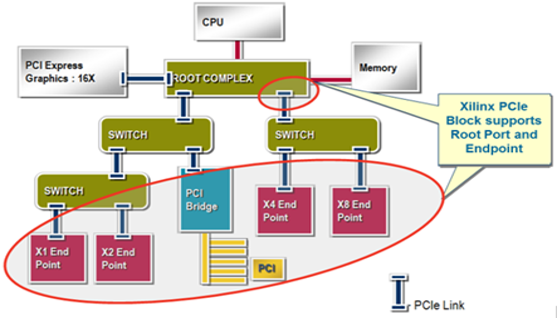

Objective: provides details about the Xilinx PCI Express® solutions.

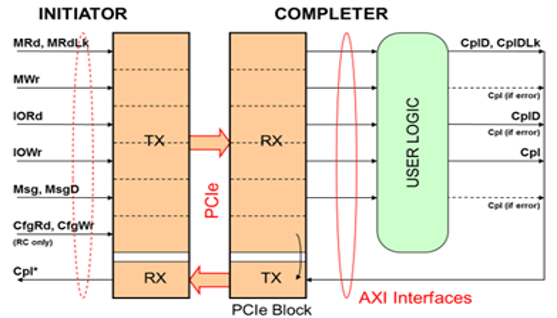

Objective: an introduction to the AXI interface from ARM.

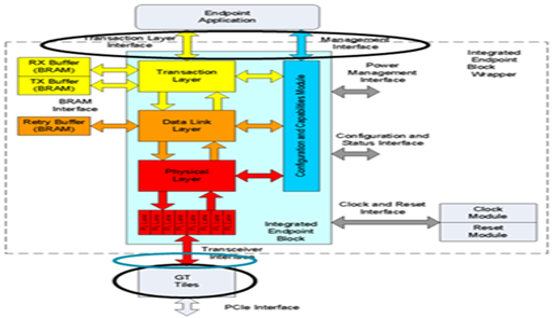

Objective: demonstrates how you can use the Vivado® IP catalog to produce a basic PCIe® endpoint core.

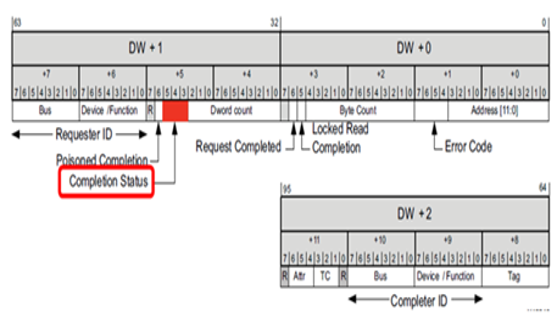

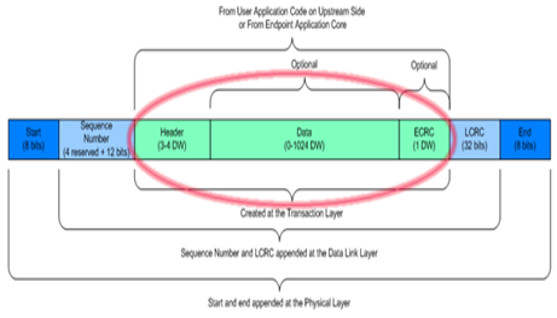

Objective: builds upon the protocol review and delves into the memory read and memory write completion details.

Objective: module covers the concepts required for conducting a full simulation.

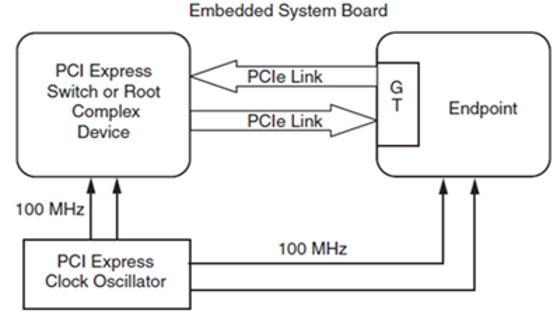

Objective: discusses important design considerations when using a PCIe® endpoint core.

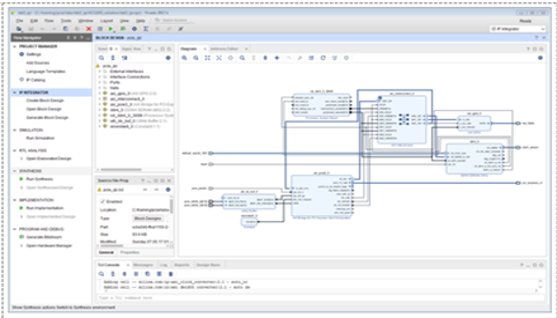

Objective: discusses the use of PCI Express® IPs in embedded designs, especially in the IP Integrator.

Objective: discusses the theory and solutions for the most commonly performed PCIe® core task.

Objective: describes the different PCIe® configuration mechanisms to meet the 120-ms PCIe core power-up requirements.

Objective: provides an introduction the root port core and its basic capabilities and applications.

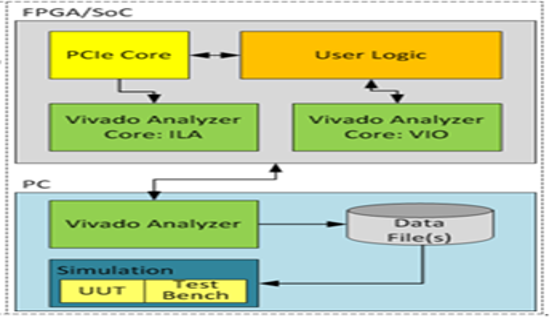

Objective: focuses on how the Vivado® logic analyzer feature can be used to monitor and, if necessary, debug the design. Other debugging options are discussed. Information about the post-design certification of the user’s design is discussed as well.

Objective: discusses the PCI Express® error management and gives an overview of interrupt options.