TechSource Systems is MathWorks Authorized Reseller and Training Partner

Learn about Versal® ACAP architecture and design methodology.

The emphasis of this three-day course is on:

What’s New for 2021.2

Software and hardware developers, system architects, and anyone who wants to learn about the architecture of the Xilinx Versal ACAP device.

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorized Reseller and Training Partner

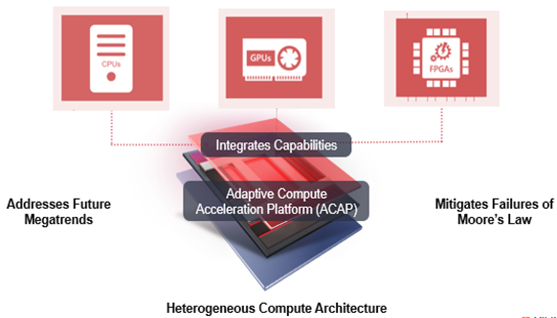

Objective: Talk about the need for Versal devices and gives an overview of the different Versal families.

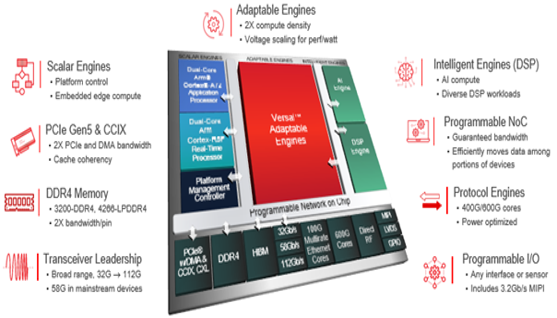

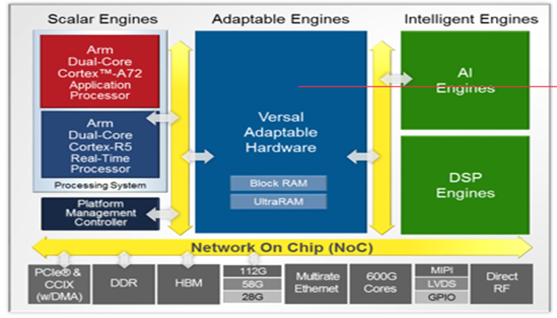

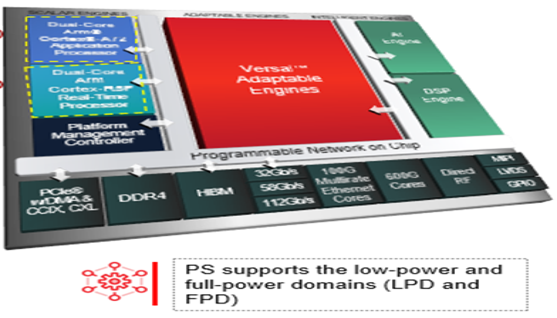

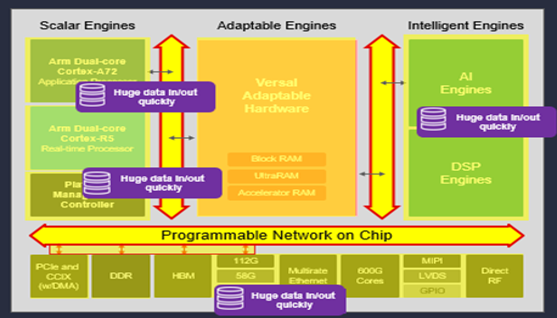

Objective: Provide a high-level overview of the Versal architecture, illustrating the various engines available in the Versal architecture.

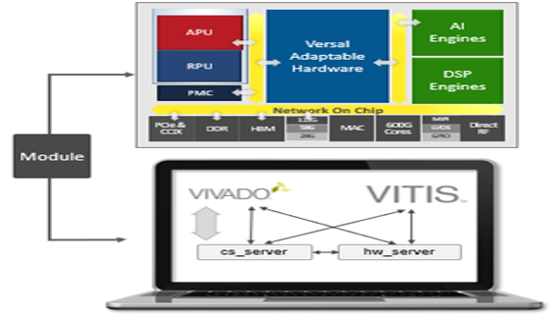

Objective: Map the various engines in the Versal architecture to the tools required and describes how to target them for final image assembly.

Objective: Describe the logic resources available in the Adaptable Engine.

Objective: Review the Cortex™-A72 processor APU and Cortex-R5

processor RPU that form the Scalar Engine. The platform

management controller (PMC), processing system manager(PSM), I/O peripherals, and PS-PL interfaces are also covered.

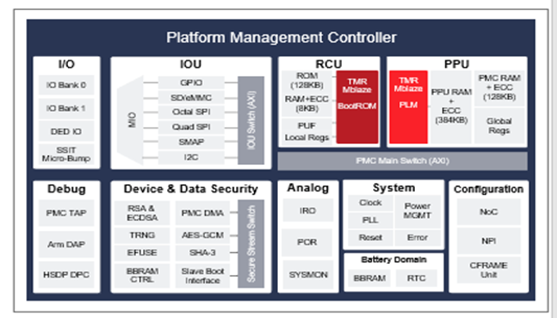

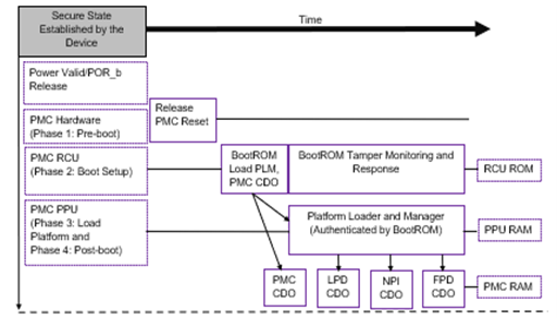

Objective: Describe the platform management controller, platform loader and manager (PLM) software and boot and configuration.

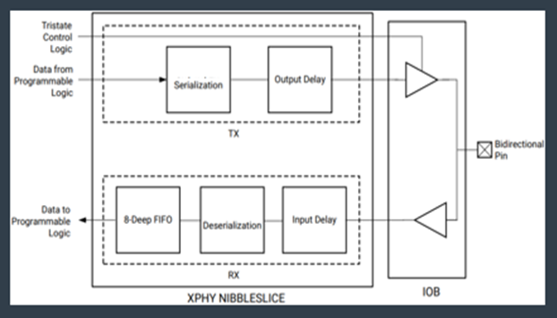

Objective: Describes the I/O bank, SelectIO™ interface, and I/O delay features.

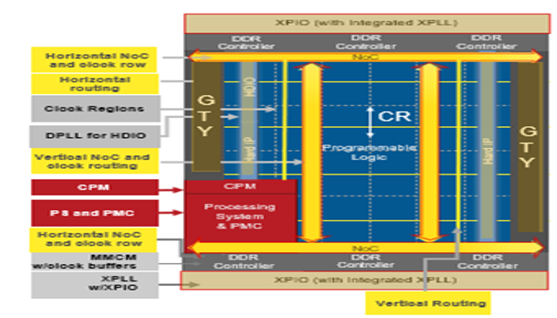

Objective: Discuss the clocking architecture, clock buffers, clock routing, clock management functions, and clock de-skew.

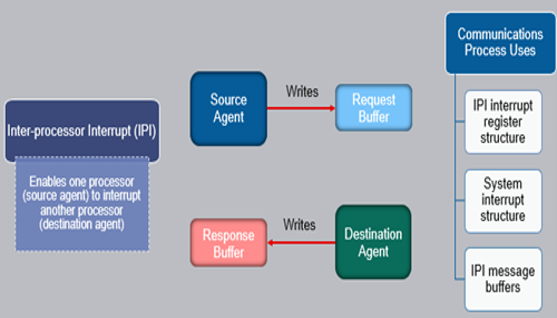

Objective: Discuss the different system interrupts and interrupt controllers.

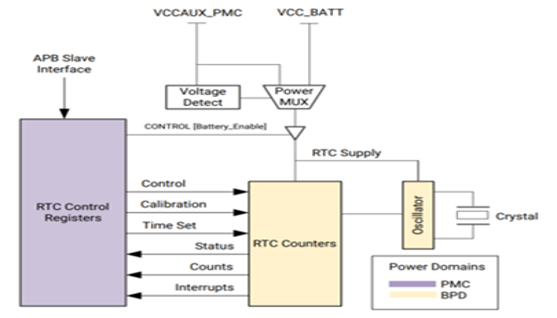

Objective: Provide an overview of timers and counters, including the system counter, triple timer counter (TTC), watchdog timer, and real-time clock (RTC).

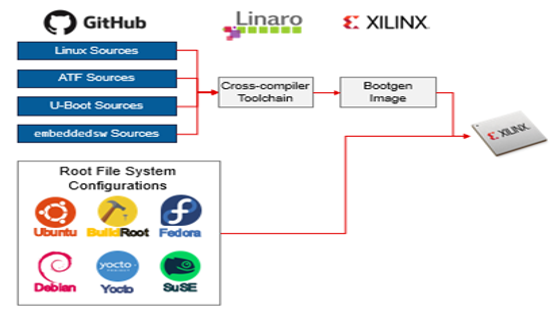

Objective: Provide an overview of the different build flows, such as the do it yourself, Yocto Project, and PetaLinux tool flows.

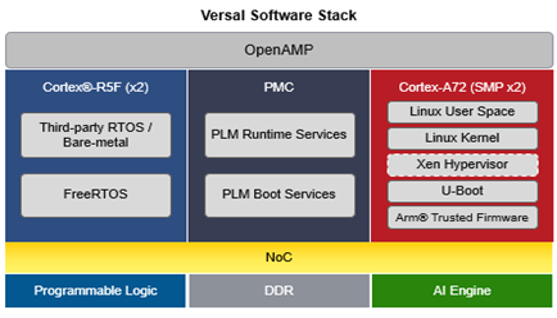

Objective: Review the Versal ACAP bare-metal, FreeRTOS, and Linux software stack and their components.

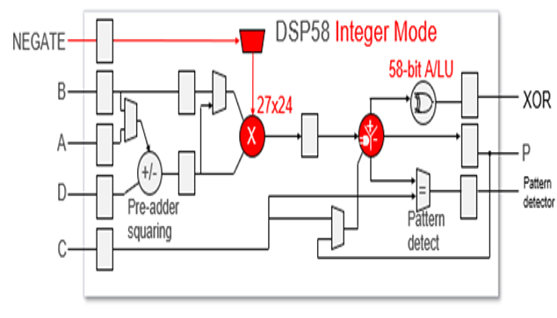

Objective: Describe the DSP58 slice and compares the DSP58 slice with the DSP48 slice. DSP58 modes are also covered in detail.

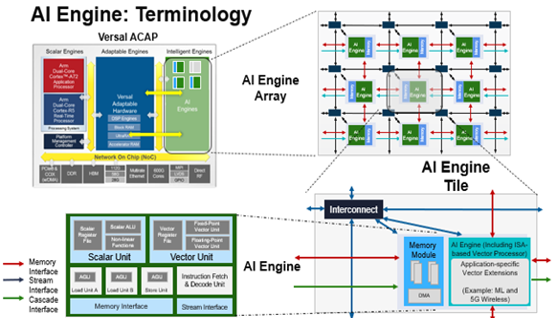

Objective: Discuss the AI Engine array architecture, terminology, and AIE interfaces.

Objective: Cover the reasons to use the network on chip, its basic elements, and common terminology.

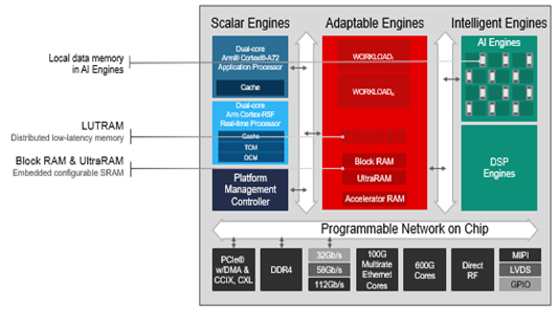

Objective: Describe the available memory resources, such as block RAM, UltraRAM, LUTRAM, embedded memory, OCM, and DDR. The

integrated memory controllers are also covered.

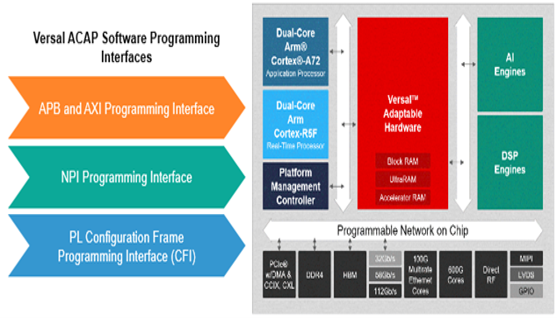

Objective: Review the various programming interfaces in the Versal ACAP.

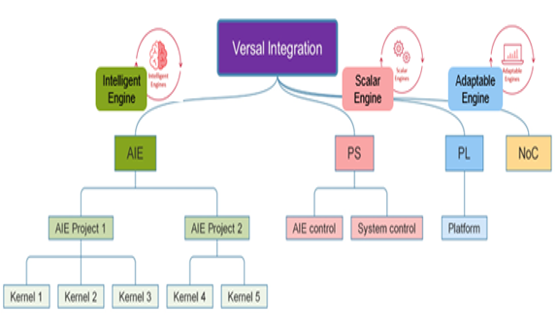

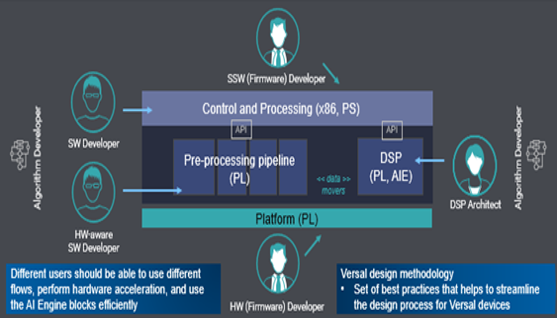

Objective: Cover what application partitioning is and how the mapping of resources based on the models of computation can be performed.

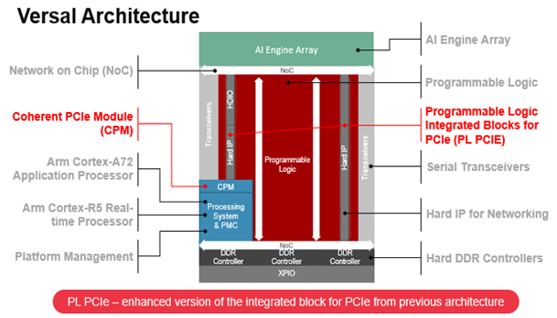

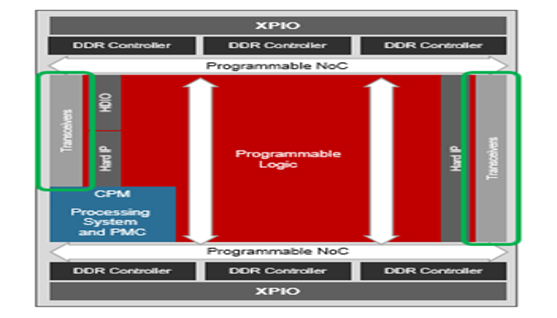

Objective: Provide an overview of the CCIX PCIe module and describes the PL and CPM PCIe blocks.

Objective: Describe the transceivers in the Versal ACAP.

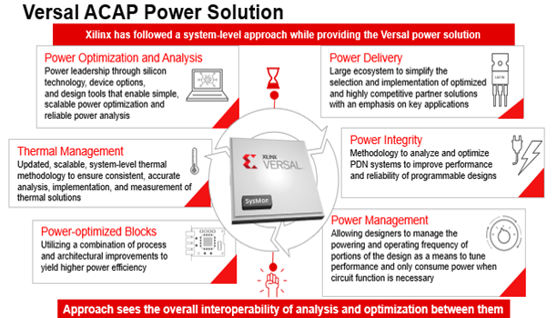

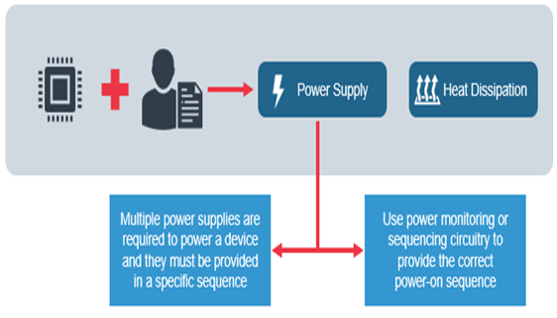

Objective: Discuss the power domains in the Versal ACAP as well as power optimization and analysis techniques. Thermal design challenges are also covered.

Objective: Cover the Versal ACAP debug interfaces, such as the test access port (TAP), debug access port (DAP) controller, and

high-speed debug port (HSDP).

Objective: Describe the security features of the Versal ACAP.

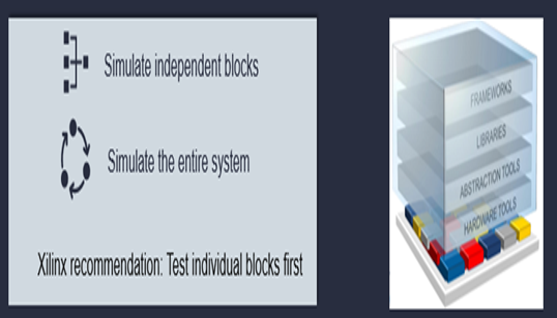

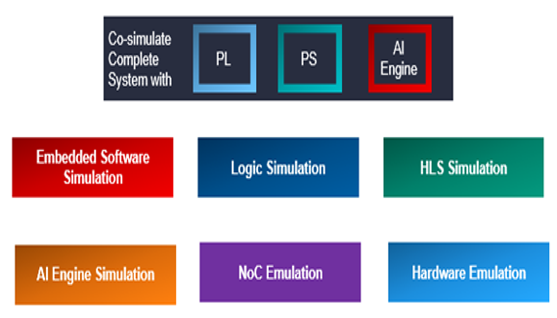

Objective: Explain how to perform system-level simulation in a Versal ACAP design.

Objective: Describe PCB, power, clocking, and I/O considerations when designing a system.

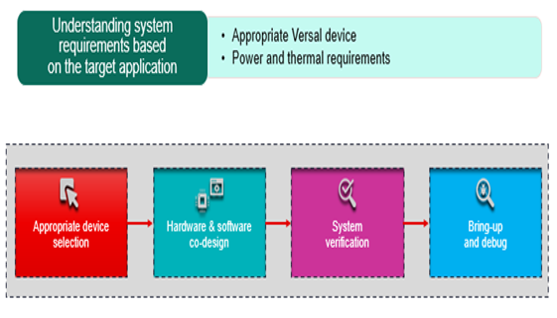

Objective: Describe design partitioning, power, and thermal guidelines. Also reviews system debug, verification, and validation planning.

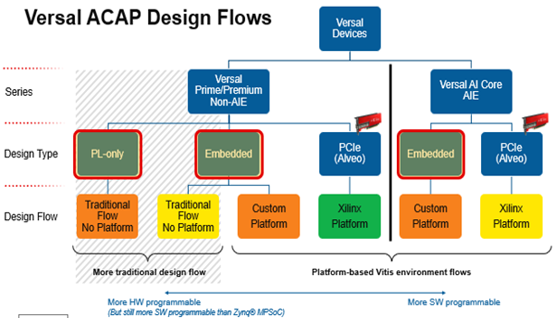

Objective: Describe the different Versal ACAP design flows and covers the platform creation process using the Vivado IP integrator, RTL, HLS, and Vitis environment.

Objective: Describe different simulation flows as well as timing and power closure techniques. Also explains how to improve system performance.