TechSource Systems is MathWorks Authorized Reseller and Training Partner

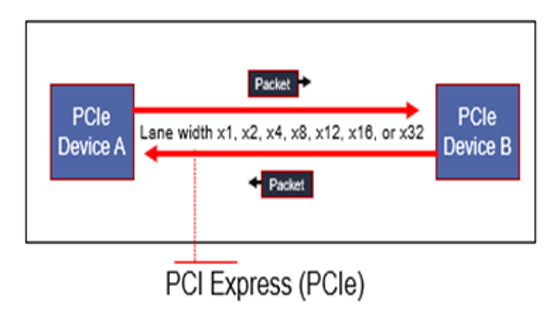

Introduces the features and capabilities of the PCIe® and

Cache Coherent Interconnect blocks in the Versal™ architecture.

This two-day course introduces the features and capabilities of the PCIe® and Cache Coherent Interconnect blocks in the Versal™ architecture. Learn how to implement a Versal ACAP PCI Express® solution in custom applications to improve time to market.

The emphasis of this course is on:

This course also focuses on the AXI-Streaming interconnect.

After completing this comprehensive training, you will have the necessary skills to construct a basic PCI Express system by:

TechSource Systems is MathWorks Authorized Reseller and Training Partner

Objective: Introduces the course and discusses a few key topics of the PCI Express protocol.

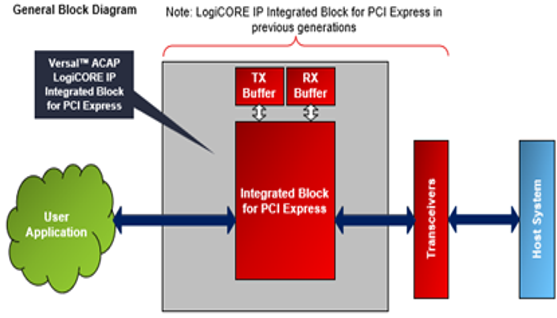

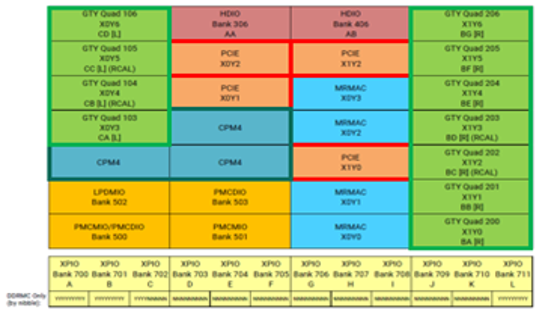

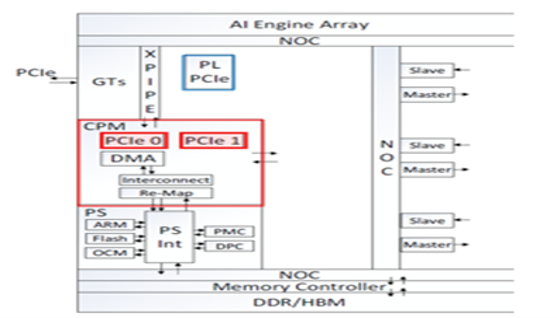

Objective: Provides an overview of the Xilinx PCI Express solutions in the Versal architecture and identifies key differentiators.

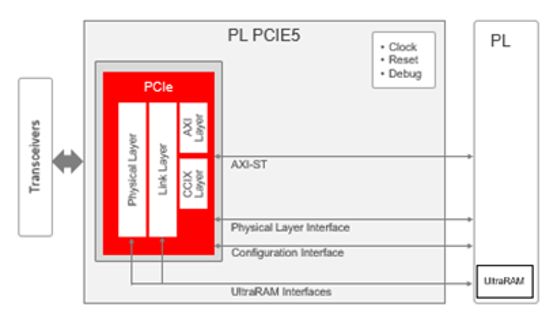

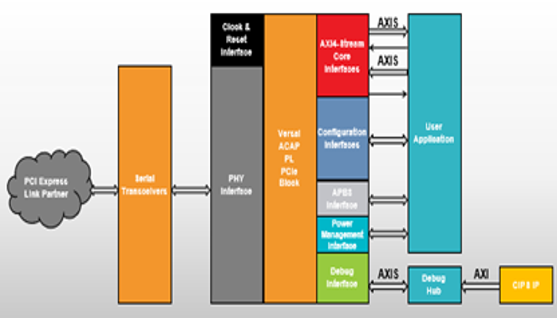

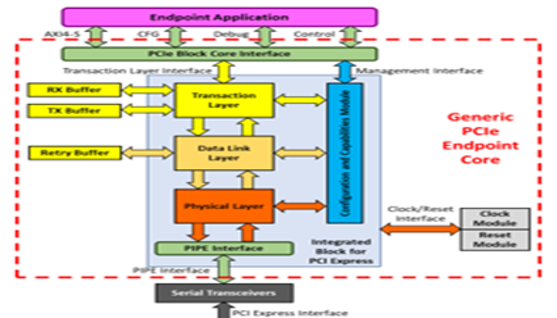

Objective: Describes the PL PCIe block architecture. You will learn details on the block features and functionality.

Objective: Provides an overview of the PL PCIe block interfaces. Deeper discussion on physical layer and general interfaces.

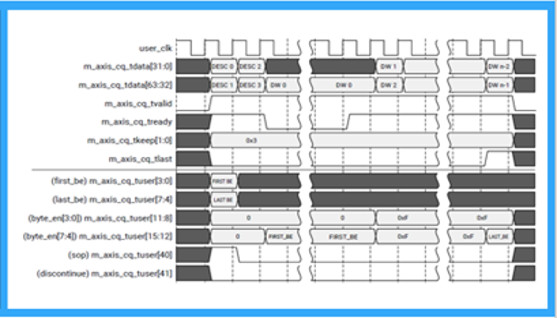

Objective: Reviews the requester AXI4-Streaming core interfaces. You will learn how to utilize packet descriptors for request interfaces.

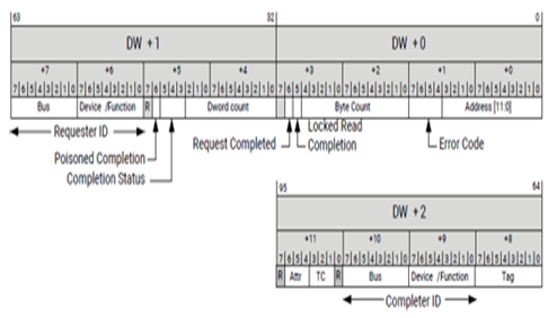

Objective: Reviews the completer AXI4-Streaming core interfaces. You will learn how to utilize packet descriptors for completion interfaces.

Objective: Illustrates customizing the PL PCIe block. You will learn how to utilize the various configuration options.

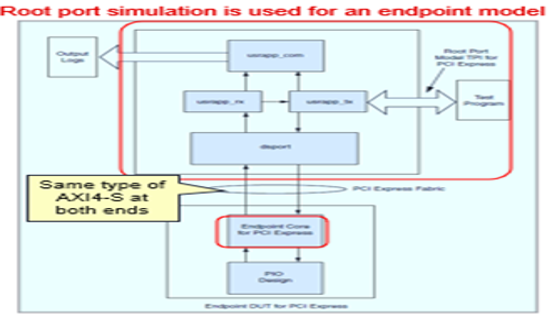

Objective: Discusses PCIe block simulation. You will learn how to utilize the generated example design to verify the functionality of the PL PCIe solution.

Objective: Discusses implementation topics. You will review the placement recommendations for the PL PCIe blocks, transceivers, clocks, and resets.

Objective: Describes the PCI Express debugging options in the Versal ACAP PCI Express physical and transaction layers. You will learn how to perform PCI Express link debug.

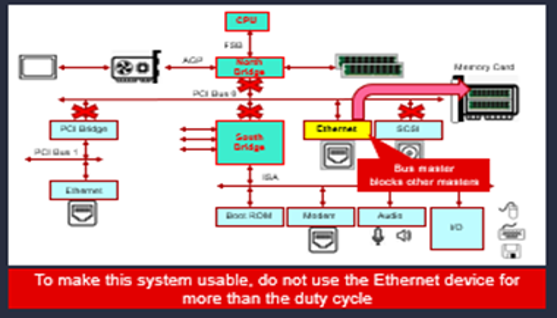

Objective: Reviews DMA basics and describes DMA in the context of the PCI Express standard.

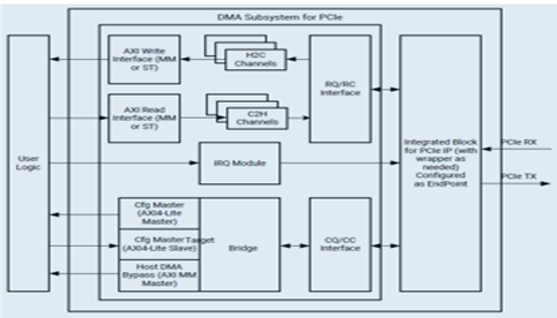

Objective: Describes the Xilinx XDMA architecture and features as well as DMA descriptor usage and interface options. You will learn how to utilize the Xilinx XDMA subsystem.

Objective: Describes the Xilinx QDMA architecture and features. You will learn how to utilize the Xilinx QDMA subsystem and its queue usage.

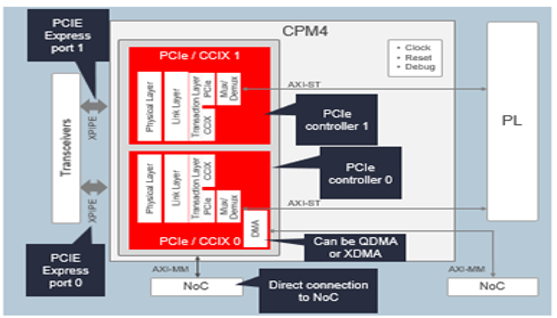

Objective: Describes the CPM4 block architecture and functionality. You will learn the commonalities and differences to the PL PCIe solution.

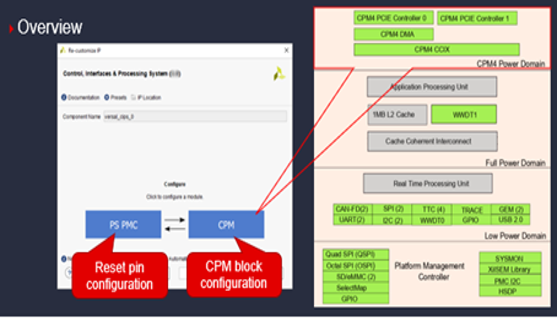

Objective: Reviews the configuration options of the CIPS CPM block. You will learn how to customize the CPM PCIe block.

Objective: Describes typical use cases for the Versal ACAP PCI Express solutions to enable you to select the right solution for your design requirements.