TechSource Systems is MathWorks Authorised Reseller and Training Partner

Enhance productivity using the Vitis Unified IDE

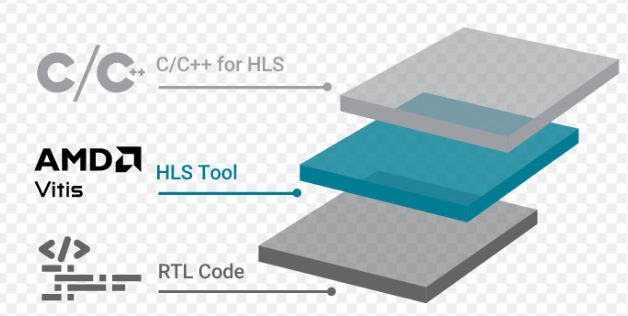

This course provides a thorough introduction to the Vitis™ High-Level Synthesis (HLS) using the AMD Vitis™ Unified IDE.

The focus of this course is on:

What’s New for 2023.2

Software and hardware engineers looking to utilize high-level synthesis

After completing this comprehensive training, you will have the

necessary skills to:

TechSource Systems is MathWorks Authorised Reseller and Training Partner

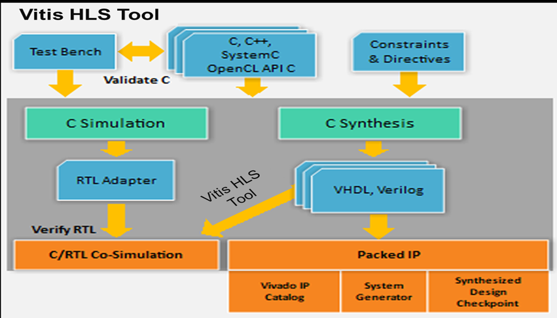

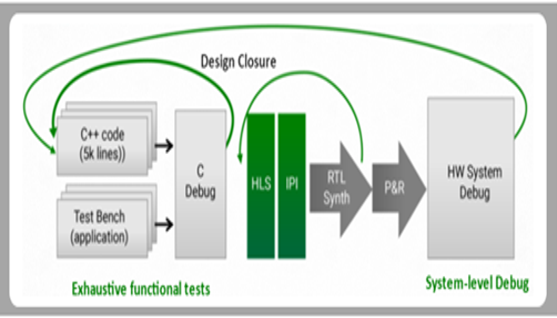

Objective: Provides an overview of high-level synthesis (HLS), the Vitis Unified IDE for HLS flow, and the verification advantage.

Objective: Explores the HLS component development flow in the Vitis Unified IDE.

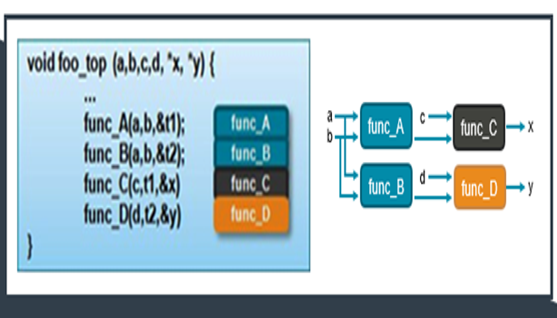

Objective: Describes the structuring of a design at a high level using an abstract parallel programming model.

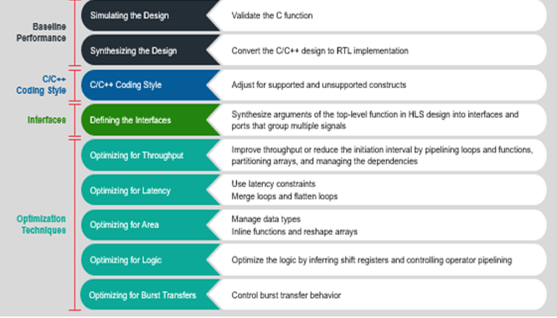

Objective: Explores different optimization techniques that can improve design performance.

Objective: Describes the unified command line interface and the the v++ and vitis-run commands.

Objective: Introduce the methodology guidelines covered in this course and the HLS Design Methodology steps.

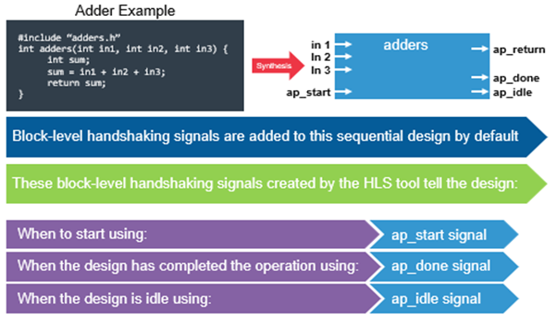

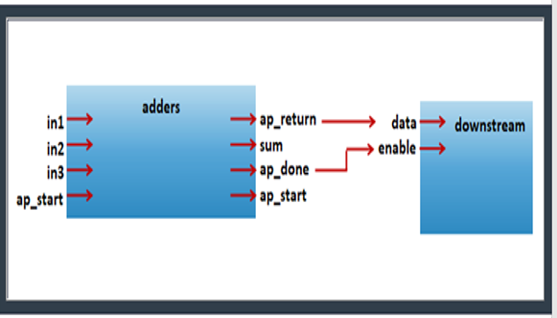

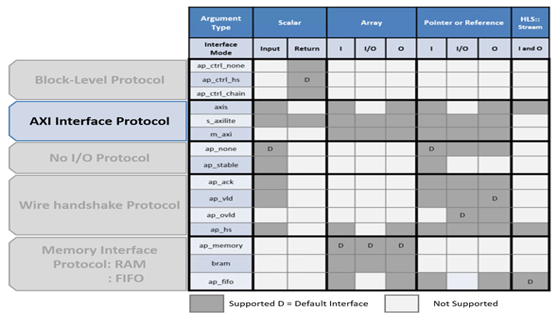

Objective: Explain interfaces such as the block-level and port-level protocols abstracted by the Vitis HLS from a C design.

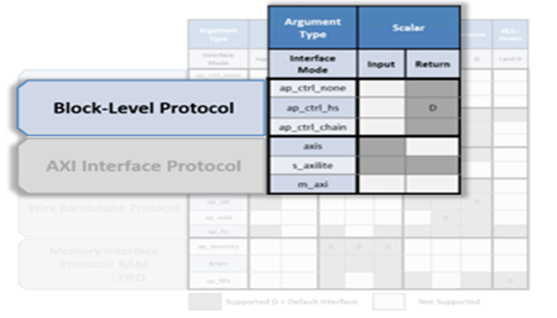

Objective: Explain the different types of block-level protocols abstracted by the Vitis HLS.

Objective: Describe the port-level interface protocols abstracted by the Vitis HLS from the C design.

Objective: Explain the different AXI interfaces (such as AXI4-Master, AXI4-Lite (Slave), and AXI4-Stream) supported by the Vitis HLS.

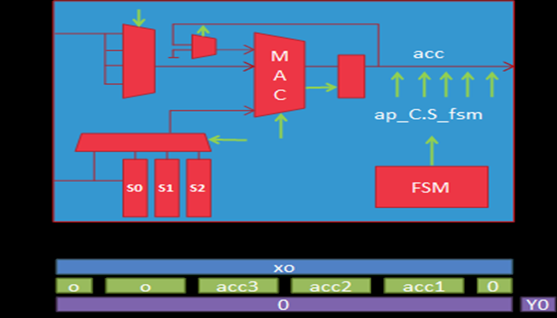

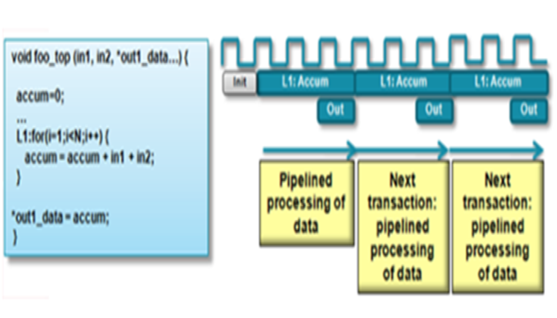

Objective: Describe the PIPELINE directive for improving the throughput of a design.

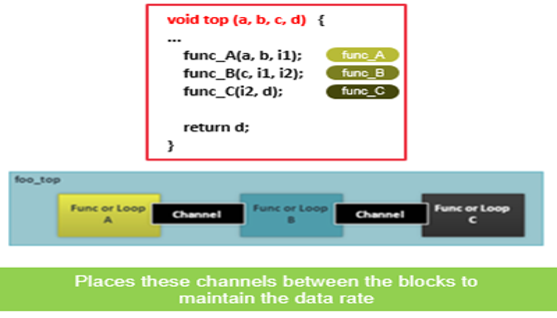

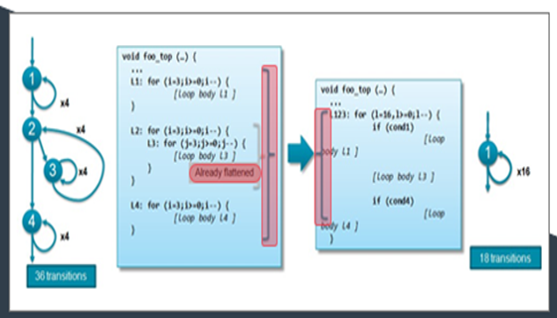

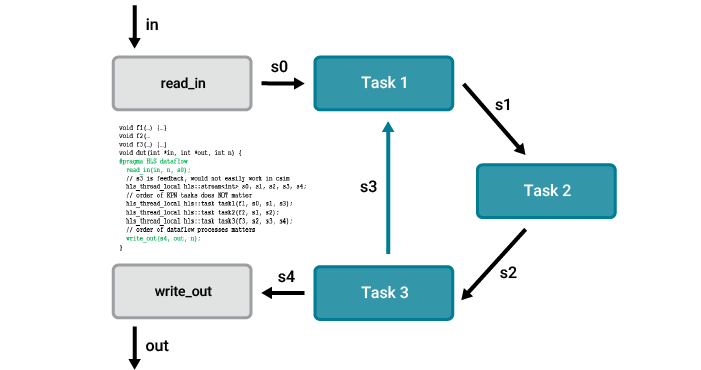

Objective: Describe the DATAFLOW directive for improving the throughput of a design by pipelining the functions to execute as soon as possible.

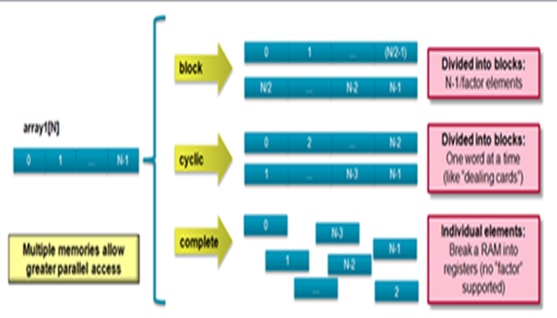

Objective: Describles the performance limitations caused by arrays in your design. Also explore optimization techniques to handle arrays for improving performance.

Objective: Describe the default behavior of the Vitis HLS on latency and throughput.

Objective: Describes how to optimize the C design to improve latency.

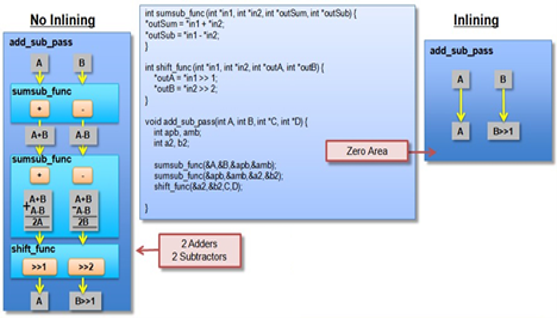

Objective: Describe different methods for improving resource utilization and explains how some of the directives have impact on the area utilization.

Objective: Describes AXI burst transfers and their types. Also outlines the optimization steps to improve system performance.

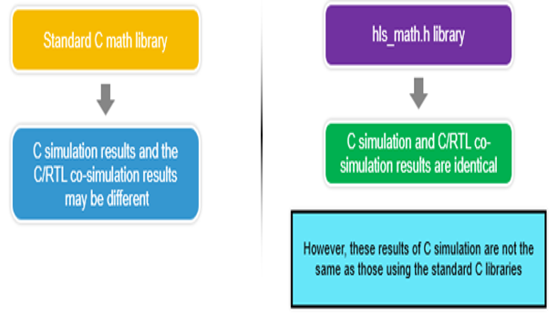

Objective: Describes the library support offered by Vitis HLS.

Objective: Describe Vitis HLS tool support for the C/C++ languages as well as arbitrary precision data types.

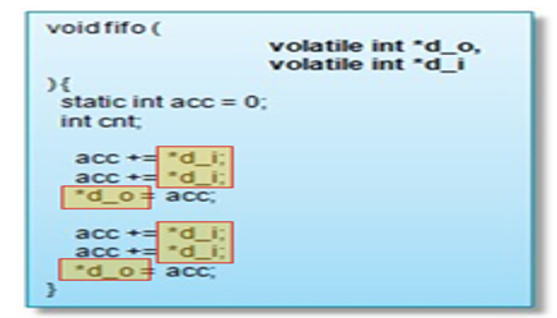

Objective: Explain the use of pointers in the design and workarounds for some of the limitations.

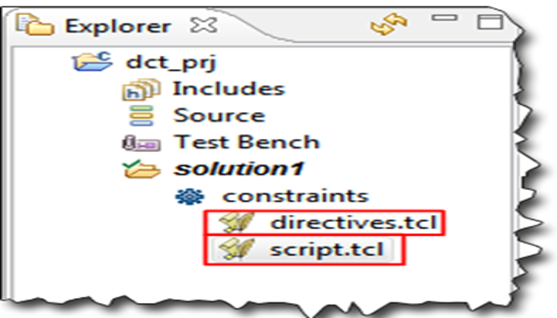

Objective: Illustrates the process of developing and exporting an HLS component as Vivado IP.

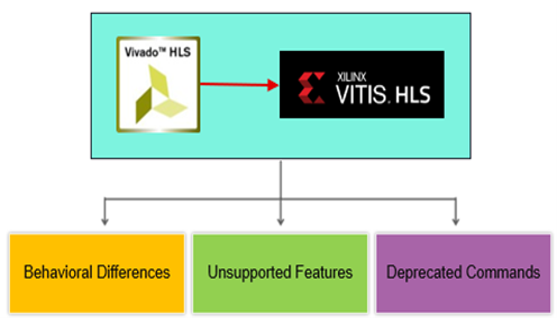

Objective: Describes the need for the Vitis Unified IDE and identifies different approaches for migrating projects from the classic Vitis HLS tool to the Vitis Unified IDE.